- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

imx6ULL EIM CS invalid

Hello everyone, my question now is that when using DMA to read data from the FIFO of FPGA on the EIM interface, both the CS signal and OE signal are normal. However, when using direct memory reading and writing, the CS signal remains invalid. Here is my code. Does anyone know what the problem is?

#define FPGA_BASE 0x50000000

#define REG_PULSE (*((volatile unsigned short *) (FPGA_BASE + 0x0002)))

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD_InitMemory();

BOARD_InitDebugConsole();

BOARD_InitModuleClock();

SystemInitIrqTable();

while (1)

{

REG_PULSE = temp;

temp = FPGA_BASE;

}

Board_ InitMemory() uses code from the official SDK and has not made any modifications。

Hello @Levear,

I hope you are doing well.

Thanks for sharing the code snippet, I checked it.

In addition to that I have a few queries to ask, Please find them below.

Which Linux BSP are you using?

What NXP EVK are you using?

Please share the dmesg logs as well as the environmental details.

Thanks & Regards,

Sanket Parekh

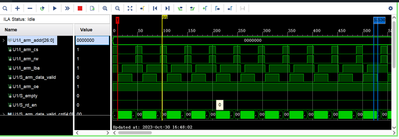

The previous issue has been resolved, it is due to the FPGA program。There is a new problem, in synchronous mode (Burst len=32), when I write data to addresses 0x50000000 (FPGA corresponding address 0x0000) and 0x50000002 (0x0001) using two variables, as shown in the following figure, the FPGA only grabs an address of 0x0000 and does not have 0x0001. However, when I replace 0x5000002 with 0x50000040, the FPGA can grab an address of 0x0020.

thank you ! you are right .

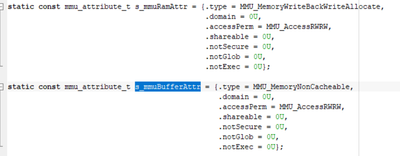

The official SDK defaults to setting memory to s_ MmuRamAttr, it should be set to s_ MmuBufferAttr, the specific differences are as follows

This way, the CS and RW signals are normal, but there is another issue: reading data is normal, but when writing data, the data received by the FPGA on the data bus is always 0, which is strange?