- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx6Q,BCLK not work

imx6Q,BCLK not work

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx6Q,BCLK not work

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

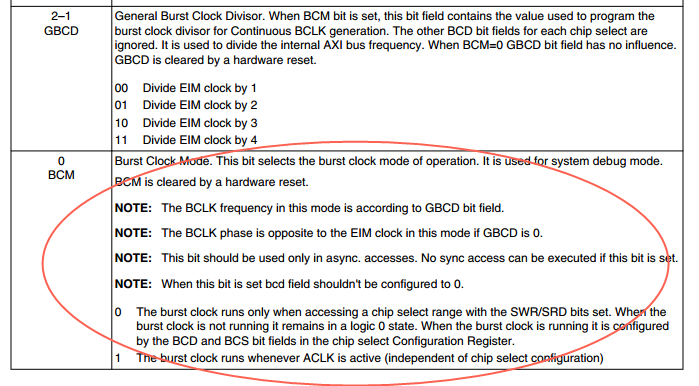

| 1 The burst clock runs whenever ACLK is active (independent of chip select configuration) |

I tried activating the BCLK continuously on my i.MX6Q board by setting ('1') the BCM bit (bit 0) on the EIM_WCR (0x021B_8090h) register.

I am not getting any clock on BLCK - constant '0'.

Did I forget anything?

here is my register configuration

MX6Q_PAD_EIM_BCLK__WEIM_WEIM_BCLK, //pin_conf

writel(0x00020081, ram_reg); //EIM_CS0GCR1

writel(0x00000001, ram_reg + 0x90); // EIM_WCR

someone help me ,what should i do to solve this problem??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

1.

What is content of the following registers?

1.1.

IOMUXC_SW_MUX_CTL_PAD_EIM_BCLK Pad Mux Register

at address: 0x020E_0158

1.2.

IOMUXC_SW_PAD_CTL_PAD_EIM_BCLK Pad Control Register

at address: 0x020E_046C

2.

According section 22.5.4 [Burst Clock Divisor (BCD)] of i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 4, 09/2017:

“The BCM bit is used mainly for system debug mode. It has no functional use of the EIM in normal mode.” Note, the i.MX6 D/Q does not have special PLL for providing continuous BCLK, synchronized with internal (system bus) ACLK. This feature is supported in i.MX6 S/DL. So, for i.MX6 DQ we cannotguarantee, that BCLK in continuous mode is fully synchronized with ACLK.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct

Answer button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello

IOMUXC_SW_MUX_CTL_PAD_EIM_BCLK Pad Mux Register

at address: 0x020E_0158

IOMUXC_SW_PAD_CTL_PAD_EIM_BCLK Pad Control Register

at address: 0x020E_046C

these two Register value is reset value ,i printed out the contents of the register,MUX_CTL_PAD(0158h) is 0 , PAD_CTL_PAD(046ch) is b0b1.

“The BCM bit is used mainly for system debug mode. It has no functional use of the EIM in normal mode.”

How do I set my board debug mode?

This feature is supported in i.MX6 S/DL. So, for i.MX6 DQ we cannotguarantee?

What does this mean? the i.mx6Q does not supported??