- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

iMX8MM-EVK LPDDR4 not work

Hi guys,

I'm used sample iMX8MM-EVK pcb from NXP to make a board, 100% like iMX8MM-EVK.

When I using MSCALE_DDR_TOOL version 310 to test LPDDR4. Calibration and street test OK. Result is attached bellow.

But, when I try to read or write ddr address (like : 0x2000000), MSCALE_DDR_TOOL alert me that MCU will be hungup. I can load imx-boot-imx8mmevk-sd.bin-flash_evk and run u-boot SPL. When I try to read or write ddram from u-boot, MCU hangup and reseting.

Can you tell me why? and how to fix it?

Thank you and br,

This my log,

Downloading file 'bin\lpddr4_train1d_string.bin' ..Done

Downloading file 'bin\lpddr4_train2d_string.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_1d_imem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_1d_dmem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_2d_imem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_2d_dmem.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m845s_ddr_stress_test.bin' ...DoneDownload is complete

Waiting for the target board boot...===================hardware_init=====================

********Found PMIC BD718XX**********

hardware_init exit*************************************************************************

*************************************************************************

*************************************************************************

MX8 DDR Stress Test V3.10

Built on Feb 5 2020 13:04:09

*************************************************************************--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug- VMCR Check:

- ttbr0_el3: 0x93d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 1800MHz

DDR Clock: 1500MHz============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 16, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 2048MB

Density per controller is: 2048MB

Total density detected on the board is: 2048MB

============================================MX8M-mini: Cortex-A53 is found

*************************************************************************

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1500Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of read DQ deskew training

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 1D-Training @200Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 1D-Training @50Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 2D-Training @1500Mhz...

[Process] End of initialization

[Process] End of 2D read delay/voltage center optimization

[Process] End of 2D read delay/voltage center optimization

[Process] End of 2D write delay/voltage center optimization

[Process] End of 2D write delay/voltage center optimization

[Result] PASS============ Step 2: DDR memory accessing... ============

Verifying DDR frequency point0@1500MHz.......Pass

Verifying DDR frequency point1@200MHz.......Pass

Verifying DDR frequency point2@50MHz.......Pass

[Result] OK============ Step 3: DDR parameters processing... ============

[Result] DoneSuccess: DDR Calibration completed!!!

DDR Stress Test Iteration 1

--------------------------------

--Running DDR test on region 1--

--------------------------------t0.1: data is addr test

....

t0.2: row hop read test

...t1: memcpy SSN armv8_x32 test

....

t2: byte-wise SSN armv8_x32 test

..

t3: memcpy pseudo random pattern test

....................................................................

t4: IRAM_to_DDRv1 test

...t5: IRAM_to_DDRv2 test

--------------------------------

--Running DDR test on frequency point1@200MHz--

--------------------------------t0.1: data is addr test

....

t0.2: row hop read test

...t1: memcpy SSN armv8_x32 test

....

t2: byte-wise SSN armv8_x32 test

..

t3: memcpy pseudo random pattern test

....................................................................

t4: IRAM_to_DDRv1 test

...t5: IRAM_to_DDRv2 test

--------------------------------

--Running DDR test on frequency point2@50MHz--

--------------------------------t0.1: data is addr test

....

t0.2: row hop read test

...t1: memcpy SSN armv8_x32 test

....

t2: byte-wise SSN armv8_x32 test

..

t3: memcpy pseudo random pattern test

....................................................................

t4: IRAM_to_DDRv1 test

...t5: IRAM_to_DDRv2 test

Success: DDR Stress test completed!!!

Hi igorpadykov,

Thanks for your reply. In two months ago, we make an other PCB for check, but it's same result.

Yes, you right. 0x2000000 is invalid address. My LPDDR4 seem be worked. I still can't boot use SDCARD or eMMC or QSPI.

When I run Linux over USB downloader UUU, it's worked. But when I set bootmode for automatic boot from sdcard or eMMC or QSPI, my custom board not work. Console not print anything.

Can you tell me how to check bootmode by bare-metal application run on iMX8M-Mini? Or anything I can do to check my custom board. Step by step bringup custom board, etc.

Thanks you.

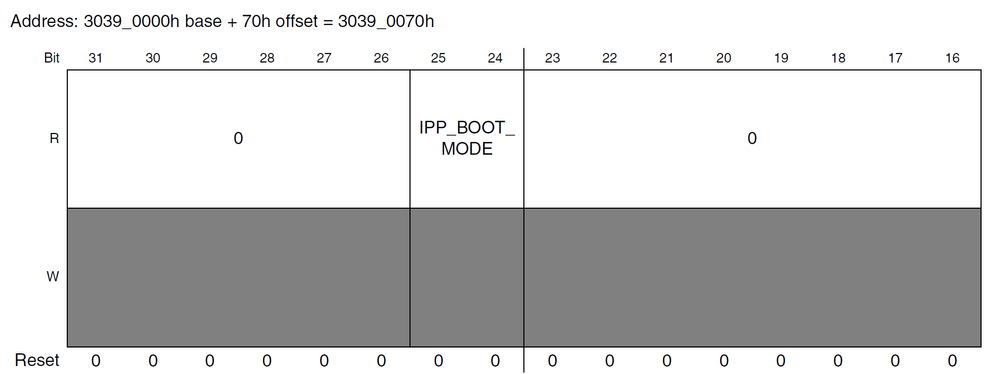

Thanks you, my bootmode wrong. It's can boot from flexQSPI now.

Hi Kieu

valid ddr memory addresses are described in sect.2.1.2 Cortex-A53 Memory Map

i.MX 8M Mini Applications Processor Reference Manual

seems 0x2000000 is not valid address. Also it is necessary to pay attention

to Chapter 4 How to bring up a new MX8MSCALE board MSCALE_DDR_Tool_User_Guide.pdf

included in ddr test package for performing necessary uboot changes.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------