- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: i.MX8MQ LPDDR4 deep sleep mode

i.MX8MQ LPDDR4 deep sleep mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

i.MX8MQ LPDDR4 deep sleep mode

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I am debugging bottom current on my board, but find the 4GByte LPDDR4 is taking much current, around 70mA from NVCC_DRAM_1V1. Then I suspect my DDR4 does not enter deep sleep mode according to its specification.

There are below registers from DDR controller:

Low Power Control Register (PWRCTL)

Hardware Low Power Control Register (HWLPCTL)

Low Power Timing Register (PWRTMG)

I tried them on uboot drivers/ddr/imx8m/lpddr4_init.c, but could not let DDR4 enter deep sleep mode after "echo mem > /sys/power/state" suspend in yocto.

Have NXP already implemented deep sleep mode? Where is the kernel code that i can try? Thanks a lot!

Wit Ding

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

Thanks for your help!

I had checked AN12118.pdf(i.MX 8M Quad Power Consumption Measurement) before, but 1.585mA does not include external LPDDR4 core current. I need find a way to let LPDDR4 to enter "Power Down Self refresh" mode. Which kernel code is responsible for this? We need change register PWRCTL, right? On mx7, it has this kind of code to do suspend in kernel, but not find for mx8m.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

imx8m sleep control PWRCTL is inside imx-atf.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Wit

Did you solve this problem?

As far as I understood, OPTEE is responsible for power management (I found code in imx-atf/plat/imx/imx8m/ddr/ddr4_dvfs.c that shoul put LPDDR4 to self-refresh mode) and it is enabled in yocto by default.

When my board booting up I saw the following lines:

- ATF b0a00f2

- U-Boot 2020.04-5.4.24-2.1.0+g4979a99482Password:

So, I suppose that OPTEE is working, but when I put processor to Deep Sleep Mode, the power consumption become 350mW (Vin=5V, Itotal=70mA) instead of 25-30mW (Vin=5V, Itotal=5-6mA)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> As far as I understood, OPTEE is responsible for power management

>(I found code in imx-atf/plat/imx/imx8m/ddr/ddr4_dvfs.c that shoul put LPDDR4 to

>self-refresh mode) and it is enabled in yocto by default.

this is not correct as OPTEE and ATF are completely different software:

https://source.codeaurora.org/external/imx/imx-atf/tree/?h=imx_5.4.24_2.1.0

https://source.codeaurora.org/external/imx/imx-optee-os/tree/?h=imx_5.4.24_2.1.0

May be useful to look at sect.5.1 Power management AN13275 How to Enable Linux BSP L5.4

> when I put processor to Deep Sleep Mode, the power consumption become 350mW

>(Vin=5V, Itotal=70mA) instead of 25-30mW (Vin=5V, Itotal=5-6mA)

sorry this is wrong measurement, as NXP guarantees power consumption in low power modes

not for all board (with Vin=5V) - this is sensless, but only for processor itself.

Please look at sect.4.1.1. Deep-Sleep Mode (DSM), sect.3.3. Voltage levels in the measurement

process

AN12118 i.MX 8M Quad Power Consumption Measurement

https://www.nxp.com/docs/en/nxp/application-notes/AN12118.pdf

So you should measure current not for all board at Vin=5V, but only on processor power

rails as described below

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

For our experiments, we use i.MX 8M Mini LPDDR4 EVK Board with imx-yocto-L5.4.24_2.1.0 release. UPD: we also tried to use mx-yocto-L5.4.70_2.3.0 release, result is the same.

We have desoldered all unnecessary components from processor board and baseboard, thus on processor board remains only CPU, LPDDR4 and PMIC. We can't add sense resistors to processor board according to the "i.MX 8M Mini Power Consumption Measurement" document, because there is no space.

When we put processor to the Suspend mode (echo mem > /sys/power/state), we see that VDD_ARM and VDD_GPU_VPU_DRAM voltages become 0V, this is consistent with clause 4.1.1 in the "i.MX 8M Mini Power Consumption Measurement" document, but the power consumption remains high (350mW as I wrote before).

I attached dmesg dump file. In the dump we find tha there is no messages about CPU0 shutdown, only about CPU1,2,3.

So now we have two ideas why power consumption in suspend mode is so high:

1) CPU0 doesn't transfer to suspend mode (doesn't shutdown according to dmesg dump)

2) LPDDR4 doesn't transfer to self-refresh mode

We found that "Power State Coordination Interface" (PSCI) in ATF is risponsible for power management features. There are functions "imx_domain_xxx" in imx-atf/plat/imx/imx8m/imx8m_psci_common.c which are responsible for transfering processor to suspend mode. Is it correct?

Also we found, that for example, for imx8mq processors functions "imx_domain_xxx" are reimplemented in file imx8mq_psci.c. Does it mean that for imx8m mini processors correct transfer to suspend mode are not implemented yet, and we should it implement it by ourselves?

We think that LPDDR doesn't transfer to self-refresh mode because ATF code (specifically bl31.bin) located in LPDDR, not int OCRAM. Is it correct? Can you provide any information about that?

Best regards,

Konstantin Ponomarev

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Konstantin

if you see "see that VDD_ARM and VDD_GPU_VPU_DRAM voltages become 0V" - then

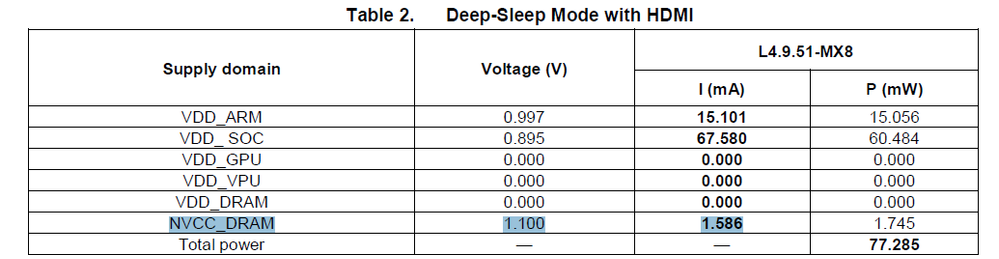

processor entered low power mode as described in Table 2. Suspend mode AN12410.

As I already answered you wrongly measured power consumption, measuring current at 5V board input.

NXP guarantees power consumption in low power modes as described in AN12410 below

>We think that LPDDR doesn't transfer to self-refresh mode..

you can follow sect.3.5. Measuring points on EVK platform and measure NVCC_DRAM current.

>We think that LPDDR doesn't transfer to self-refresh mode because ATF code

>(specifically bl31.bin) located in LPDDR, not int OCRAM. Is it correct?

not sorry.

In general you are not first who measure processor low power currents just at input of board power adapter.

For such cases NXP specially developed AN5381 Measuring Current in i.MX Applications

and special i.MX8M Plus board for low power measuerents:

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

also 350mW@5V means 70mA, assuming that you are using two boards (baseboard and SOM)

if you see linux logs, total number of resistors is about 1000, not saying about internal pull resistors.

So neceessary to verify that all of them do not draw current (not were in low state), as 70mA/1000=

70uA per resistor can be easily reached in worst case of course.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Wit

one can check sect.4.1.1. Deep-Sleep Mode (DSM) AN12118

i.MX 8M Quad Power Consumption Measurement

https://www.nxp.com/docs/en/nxp/application-notes/AN12118.pdf

test with Demo Images from i.MX Software | NXP

Sources are described in sect.2.5 Power Management Linux Manual

in Linux L4.14.98_2.0.0 Documentation

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------