- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX6SDL External Clock signals and FREER_

i.MX6SDL External Clock signals and FREER_

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

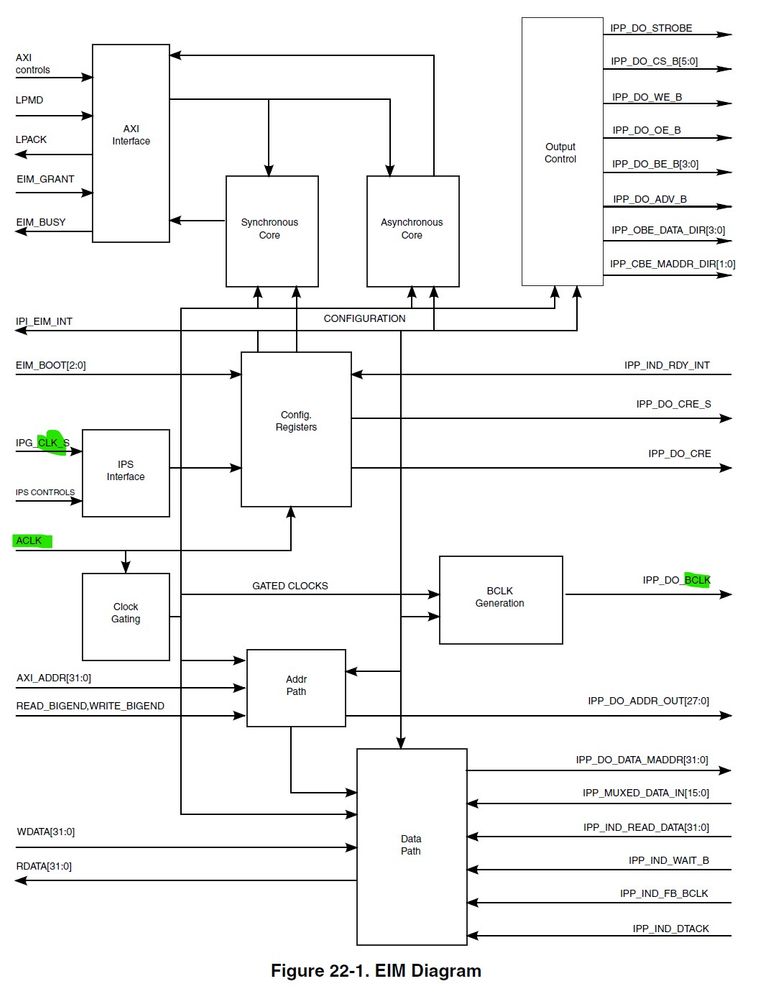

I'm trying to understand the clocking of the EIM bus with respect to the free run input clock. How exactly is this set up. I would like to output this clock signal on the observability CLKO 1 or 2.

INTENTION:

Utilize EIM_ACLK_FREERUN and continuous burst to work with non muxed Address/Data lines to a CPLD and FPGA. This clock is 43.75 MHz for legacy equipment, and I want to minimize impacts on other devices.

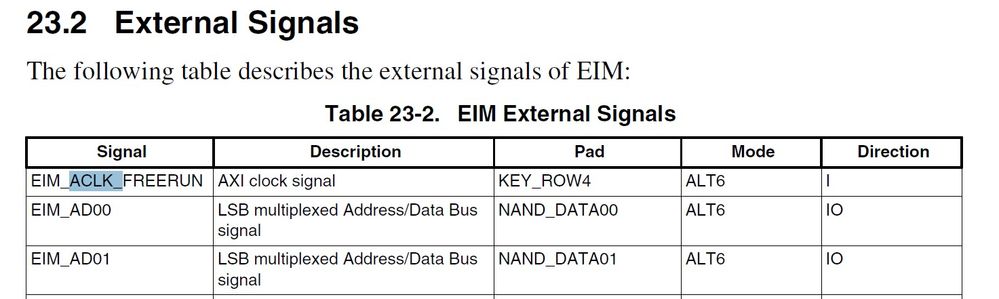

The external signals to the EIM are defined in "Table 22-2 EIM External Signals" EIM_ACLK_FREERUN and can be input via pads: EIM_A25, EIM_D31, EIM_EB3.

Current Understanding:

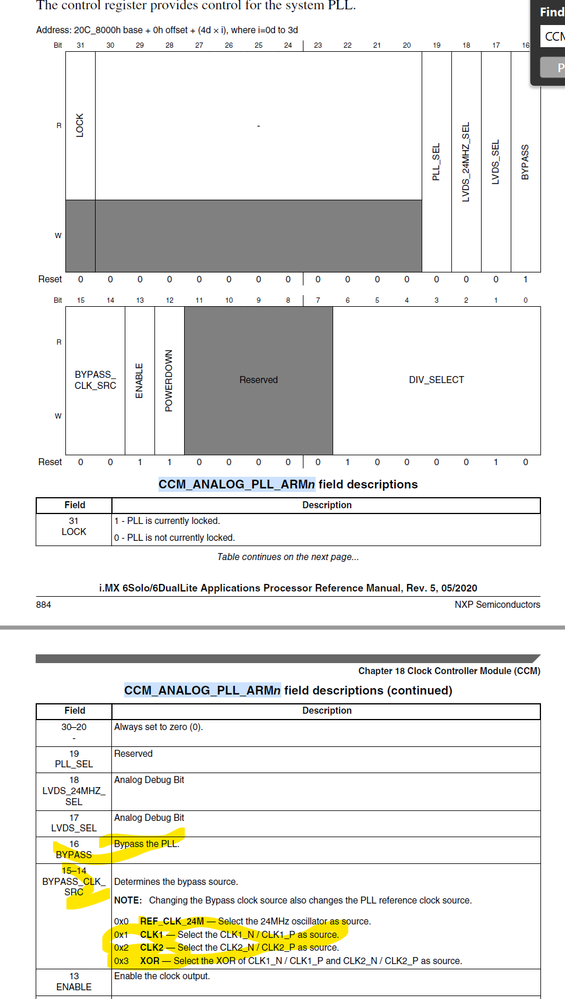

INITIALLY I thought the PLL3 bypass would allow selection of the FREERUN PIN. HOWEVER, it does not appear that this is passed through the CCM_ANALOG module to the CCM_CLK_SWITCHER. And then onto ACLK_EIM_SLOW_CLK_ROOT.

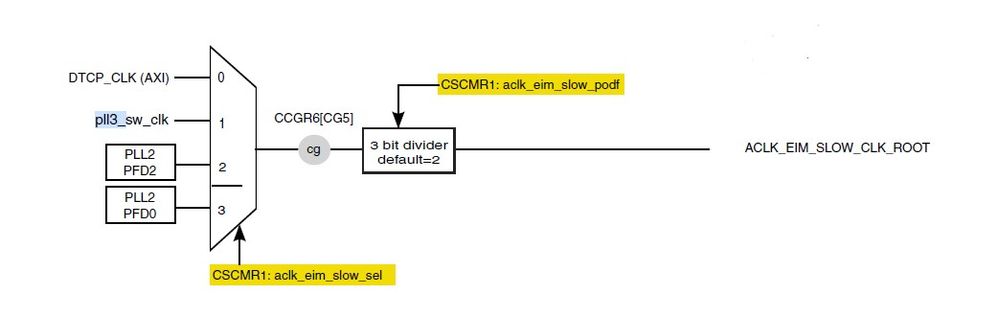

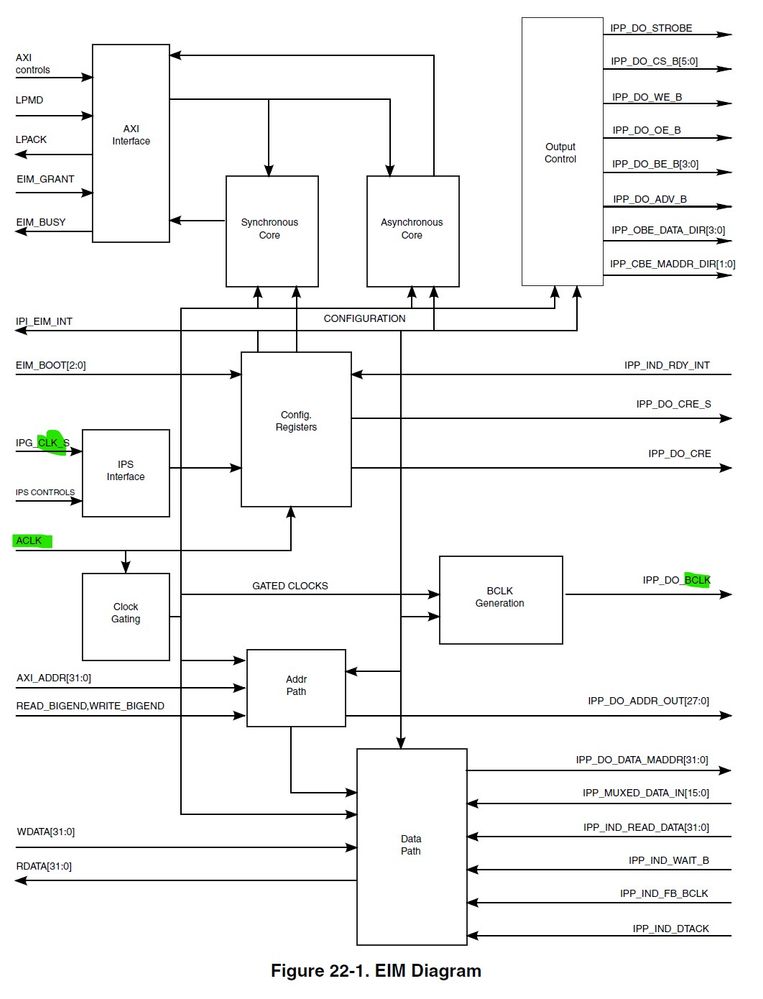

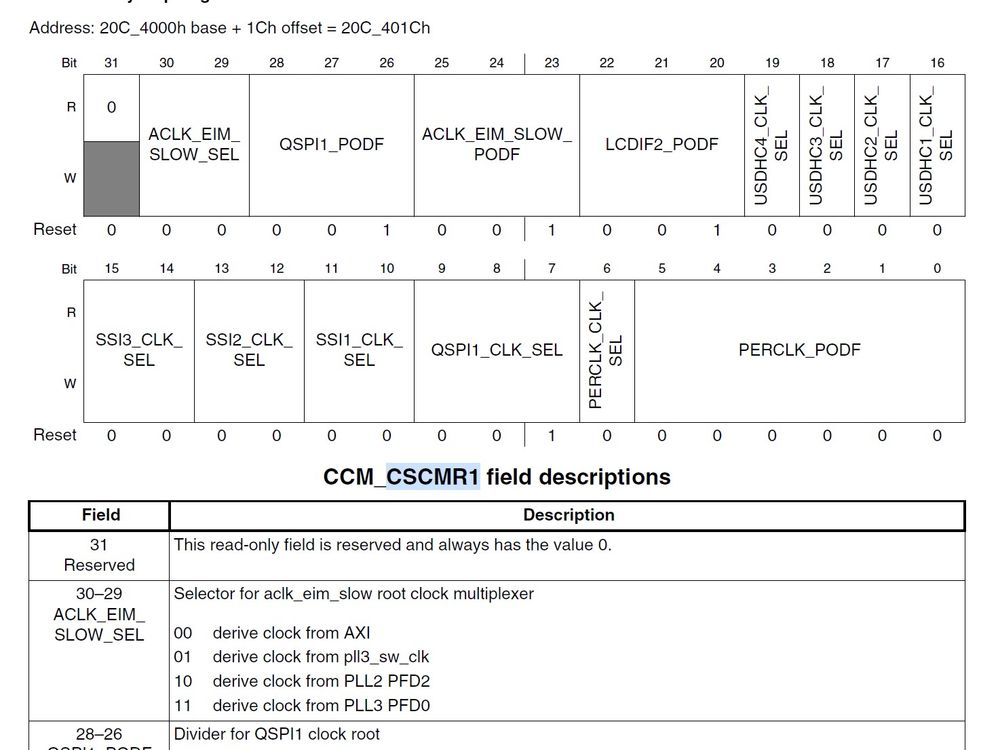

Section 22.3 Clocks: sources for EIM see CCM, Table 22-4 shows 4 possibilities with two clock roots: aclk_eim_slow_clk_root and ipg_clk_root.

aclk, aclk_slow, and aclk_exsc EIM clocks with root: aclk_eim_slow_clk_root.

HOWEVER, https://community.nxp.com/t5/i-MX-Processors/Using-ACLK-EXSC-for-the-iMX6-EIM-bus/m-p/490804

Indicates BCLK can not be configured as aclk_exsc. leaving just aclk, and aclk_slow.

GOOD NEWS it also indicates aclk_eim_slow_clk_root can be output on CCM_CLKO 1 or 2. So we get observability of aclk_eim_slow_clk_root.

Here I do not see how the free run clock can be an input to generate the ACLK_EIM_SLOW_CLK_ROOT i'm looking for.

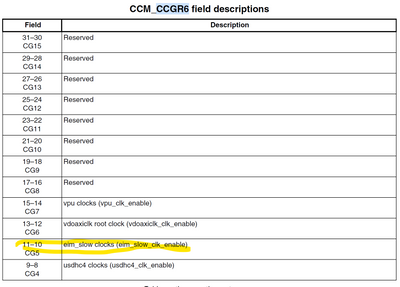

CCGR6[CG5] emi_slow_clk_enable

YET the EIM module clearly shows that the FREERUN CLOCK can be selected. Does this follow some other path through the SoC?

Yet in section 22.9.7 EIM Configuration Register (EIM_WCR)

Bit 11: FRUN_ACLK_EN

enables: Free run ACLK enable.

So my confusion is why is the FRUN_ACLK_EN and it's routing potentially through PLL3 Bypass not documented - it is hard to figure out the routing of the signals and how to make it visible on CLKO1/CLKO2.

Any clarifications appreciated.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following up, I received this reply from NXP technical support.

Please find a response from the internal Team below.

The EIM_ACLK_FREERUN direction should be O instead of I. The RM is incorrect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following up, I received this reply from NXP technical support.

Please find a response from the internal Team below.

The EIM_ACLK_FREERUN direction should be O instead of I. The RM is incorrect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This may be the solution utilize the FRUN clock in the EIM while blocking (gating the emi_slow_clk) ? :

Selecting the FRUN_ACLK_EN input to the EIM

&& Disabling the CCGR6[CG5] emi_slow_clk_enable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any updates? Seems determining how the FREE RUN clock is gated with the EIM is impossible given the state of the documentation.

What if I used CLK 1 or CLK2 and pass to PLL3 bypass then to the EIM Root clock?

How does that affect the AIX bus ? Does/would this slow my core processor clock at all?

Note desired core clock is 1GHz, and desired EIM clock is 43.75 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've begun doubting the EIM_ACLK_FREERUN Pin configuration to actually reach the EIM bus (due to lack of documentation in the CCM for handling this signal muxing and gating and scaling it at all).

For now: I will investigate the CLK1/CLK2 bypass on PLL3 to the EIM root clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For now the only routing I see for the ACLK_EIM_SLOW_SEL[30:29] that makes sense is to use the bypass on PLL3 (pll3_sw_clk) and somehow have the FREE_RUN clock go through this bypass. Or from AXI. I'm not sure of the downsides of AXI/AHB bus clocks.

Somewhat obvious concern is if it is only the AXI bus running at the Free run clock (43.75) in our case is the impact on the AMBA/AXI Arm A9 Core speeds. Would this throttle all of our operations?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the following table diagrams (imx6sx)

It appears that the AXI clock signal is tied to the EIM clock

Does that mean when I enable Bit 11: FRUN_ACLK_EN

That the AXI clock will be slaved to the FREE RUN CLOCK?