- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- i.MX6SDL EIM synchronous access when BL=Continuous burst length.

i.MX6SDL EIM synchronous access when BL=Continuous burst length.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi community,

Our partner have some questiosn about i.MX6SDL EIM.

They understand the EIM access will be burst when BL=Continuous burst length and APR=0 (synchronous access).

Then, please see their questions as following.

[Q1]

The finish timing of burst access is handled by i.MX6 EIM if WFL=1 and RFL=1.

Is this correct?

[Q2]

With the condition of Q1, software can execute a fix length access (e.g. single access).

Is this correct?

[Q3]

The finish timing of burst access is handled by EIM slave if WFL=1 and RFL=1.

Is this correct?

[Q4]

With the condition of Q2, EIM slave finishes a access by WAIT signal.

Is this correct?

Best Regards,

Satoshi Shimoda

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Satoshi

RFL,WFL do not have relation to burst behaviour.

RFL,WFL=0 means that supported WAIT signal, it is

checked after RWSC/ WWSC cycles.

RFL,WFL=1 means that WAIT signal is ignored , burst (if any,

may be just one access, that is single beat in burst)

starts after RWSC/ WWSC cycles.

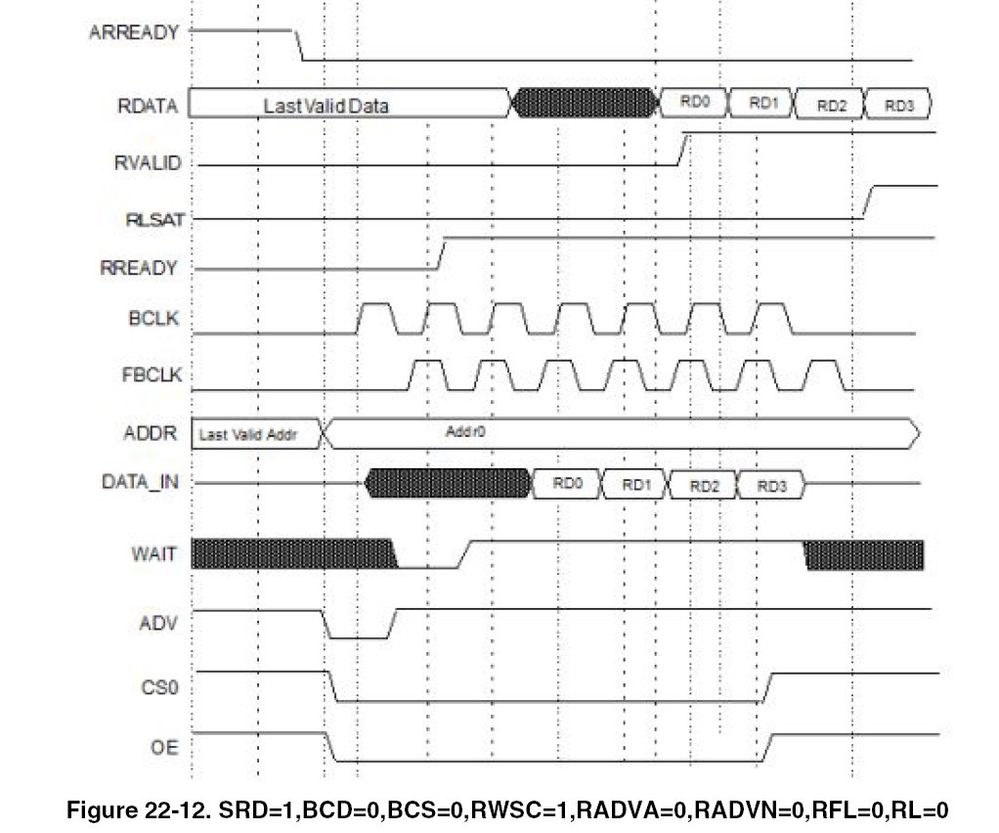

IMX6SDLRM Figure 22-12 shows such waveforms

IMX6DQRM p.1047 Figure 22-12 gives example of "burst length =4" -correspond

to RD0,1,2,3 and "number of skipped BCLK =3" : 2 - WAIT and one due to RWSC=1.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Satoshi

RFL,WFL do not have relation to burst behaviour.

RFL,WFL=0 means that supported WAIT signal, it is

checked after RWSC/ WWSC cycles.

RFL,WFL=1 means that WAIT signal is ignored , burst (if any,

may be just one access, that is single beat in burst)

starts after RWSC/ WWSC cycles.

IMX6SDLRM Figure 22-12 shows such waveforms

IMX6DQRM p.1047 Figure 22-12 gives example of "burst length =4" -correspond

to RD0,1,2,3 and "number of skipped BCLK =3" : 2 - WAIT and one due to RWSC=1.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------