- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX RT1064 LPSPI3 slave EDMA mode transmit issue

i.MX RT1064 LPSPI3 slave EDMA mode transmit issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX RT1064 LPSPI3 slave EDMA mode transmit issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I’m using i.MX RT1064 LPSPI3 as slave EDMA mode.

At first, the LPSP3 cannot work at all. It works after I updated the fsl_iomuxc.h according https://community.nxp.com/t5/i-MX-RT/LPSPI3-slave-on-GPIO-AD-B1-doesn-t-receive-data/m-p/902162.

Change:

#define IOMUXC_GPIO_AD_B1_15_LPSPI3_SCK 0x401F8138U, 0x2U, 0, 0, 0x401F8328U

to

#define IOMUXC_GPIO_AD_B1_15_LPSPI3_SCK 0x401F8138U, 0x2U, 0x401F8510U, 0x1U, 0x401F8328U

Now, my issue is:

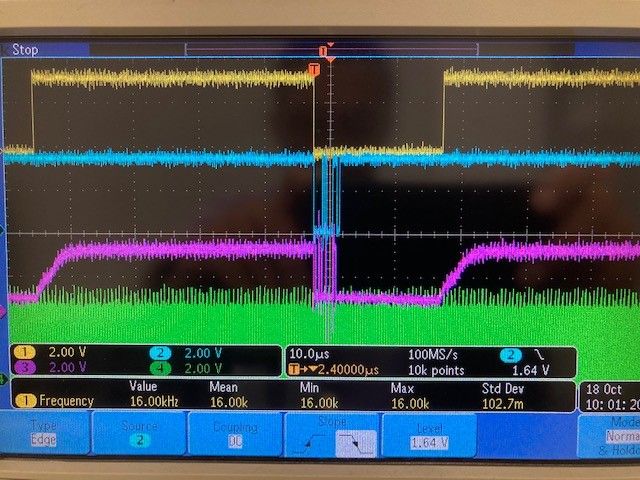

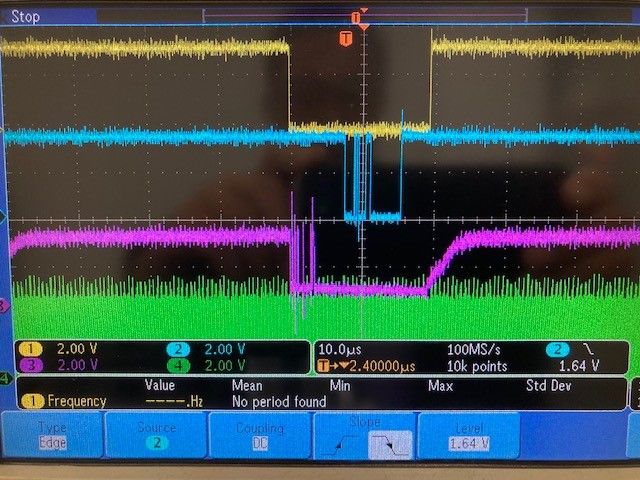

The data send form 1064 is not always start at the CS signal change to low

Data sent out when CS change to low

Data not sent out immediately when CS change to low

My purpose is to send the data when CS changed to low immediately.

Somebody can tell me how to fix this issue?

Thank you very much!

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @martinzhang ,

Thanks for your interest in the NXP MIMXRT Product, I would like to provide service for you.

Normally, it is determined by your slave code data buffer is filled or not.

Do you check the CS pull relationship with the CLK?

As you know, CLK, CS is provided by the master, so if your CLK is output directly after the CS pull low, then the issue is in the slave side, but if the CLK even not output after the CS pull low, then issue is in the master side.

Now, take your CLK is output immediated after CS pull low as an example.

Normally, I will fill the slave SPI data buffer before the master CS pull low and sendout the CLK, so, in your slave chip code, after boot, slave do the sendout at first, that will fill the slave data fifo buffer, when the master send clock after CS pull low, the slave MISO will output the data.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kerry,

Thank for your reply!

Maybe I didn’t explain my issue clearly:

In my project,

1. SPI master send data to SPI slave in short time interval,

2. Data sent to master should at the beginning of the CS pull to low

Your suggestion that put data into FIFO before master CS pull low is right, but it is hard for me to put the data into FIFO before the CS pull low.

My solution is to use anther GPIO pin to detect the CS signal, if the CS changed to high, I put the data into SPI FIFO and wait to send at next data exchange.

My solution is work, but my question is:

Is there any other easy way to implement it, such as change the setting of SPI module?

Best Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @martinzhang ,

Thanks for your updated information.

After get your information, I check the RT1064 LPSPI register again, just find one bit:

AUTOPCS, Setting the Automatic PCS bit will cause the LPSPI to generate an internal PCS signal at the end of each transfer word when the Clock Phase bit TCR[CPHA] = 1.

this is also not your used function.

So, if you need output the data immediately after get the CS pull low in the slave.

I think, your method is also useful. Or you need to combine with the master, make sure you fill the buffer before the master is send data. You can fill the data buffer when no master request data, just prepare it.

Wish it helps you!

Best Regards,

Kerry