- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

i.MX RT1020 MII Speed Control Register (MSCR)

Good morning,

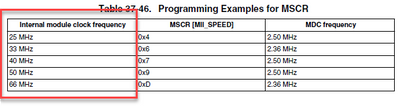

In man §37.5.1.8 ENET "Internal module clock frequency" (MDC pin, clock for MII/RMII interface), which clock does the table refer to (Internal module clock frequency) please ?

Regards

Jean-François

Hi, Thanks, not really, in the #define i see 3 sources, i couldn't get a clear reading which those drive in the chip:

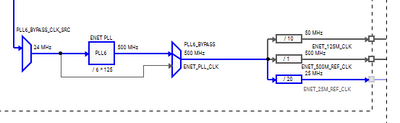

From clock setup in MCU expresso:

BOARD_BOOTCLOCKRUN_ENET_125M_CLK

BOARD_BOOTCLOCKRUN_ENET_25M_REF_CLK

BOARD_BOOTCLOCKRUN_ENET_500M_REF_CLK

The clock you refer to seems derived from BOARD_BOOTCLOCKRUN_ENET_125M_CLK but i couldn't see this in the man, except i missed something ?

Regards

Jean-François

To be more specific it refers to the reference clock. Regarding those macros, the frequency will depend on your phy. If your PHY uses 50MHz ref clock then the 125M clock will be the MAC.

If Reference clock is input then the frequency is the MAC clock:

Best regards,

Omar

Hello

Hope you are well.

It refers to the MAC clock referred on table 37-46:

Best regards,

Omar