- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

TCP Ethernet Lwip - No issue with SRAM_DRAM but issue with BOARD_SDRAM

Hi,

We have two projects developed on MCUXpresso IDE v11.8.0, SDK 2.14.0, imxRT1064. In both projects, we implemented a TCP client over Ethernet.

In the 1st project, SRAM_DRAM was used as the default RAM, and in the 2nd project, BOARD_SDRAM was used.

A task was created for the TCP client with xTaskCreate with a PRIORITY value of 3 and a STACK SIZE of 1024. There are no other tasks in the project.

After the TCP client connects to the server, it periodically sends two packets every second. The size of the first packet is 1518 Bytes and the size of the second packet is 962 Bytes. There is a 200 millisecond wait between the first packet and the second packet.

pseudocode:

send packet1

wait 200ms

send packet2

wait 1000ms

While the same codes do not cause any problems in the 1st project (the project where the default ram is SRAM_DTC), the blockage occurs after the 6th or 7th cycle in the 2nd project (the project where the default ram is BOARD_SDRAM).

The application remains in the send function. When we make the socket non-blocking, the EAGAIN value is returned. (Client algorithm closes the socket and restarts the algorithm when the send function returns a value less than 0)

Heap_3.c was used as the Freertos heap scheme.

Please see attached lwipopts.h and FreeRtosConfig.h files of the error-producing project.

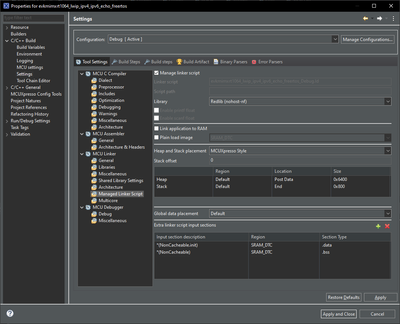

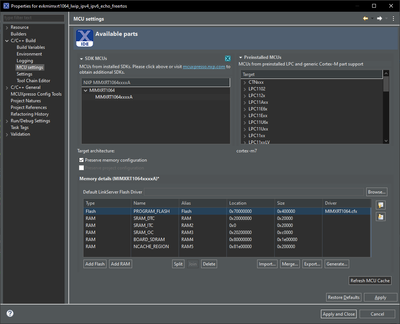

Also find attached the Heap and Stack Placement and MCU settings screenshots of the both projects.

Could you please help me about how we can solve this issue? Thanks.

1st project heap and stack:

1st project mcu settings:

2nd project heap and stack:

2nd project mcu settings:

Hello,

Thank you in advance for contacting NXP support.

Regarding your case I understand that you have no troubles on your original configuration, and you are currently trying to move your project to the BOARD_SDRAM example.

If is this the case can you please help me with the following points that are necessary in order to perform this change:

- To enable the SDRAM, it is necessary to add the XIP_BOOT_HEADER_DCD_ENABLE=1 in the following location C/C++ Build > Settings > Preprocessor, then the ROM code will fetch the DCD to initialize the SDRAM during the boot-up process.

- It is also require to link the application to RAM I attached an image for reference.

I also attached a link to a community post that can be helpful for your implementation.

Please let me know if there is anything else where I can help you.

Thanks for the reply @nxf77486 !

We made the RAM settings as seen in the 1st image.

And we set the necessary preprocessor directives as in the second image.

But when we try to debug, it either freezes or gives errors like in the 3rd image.

Hello,

Thank you in advance for the information can you please share with me. Can you please help me by following the next guide for RAM and XIP Code on i.MXRT1064. I believe this could be useful and solve the current problematic.

Thanks @nxf77486

We have tried the guide in the link but it didn't solve the issue.

You have asked to me to share, so I have created a private ticket yesterday with the firmware attached.

I appreciate if you could give us further support. Thanks!