- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Could some explain this please.. .I'm looking at DTS for my NXP SoC and a COM/board, trying to locate some peripherals and checking addresses.

What I cannot understand is what I see in DTS/Linux addresses vs what they are in SoC User guide, i.e. physical devices per NXP guide.

So e.g.:

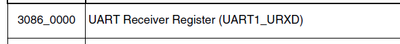

What I thought / expected to see is something like , for serial 0 as UART1 address i.e :

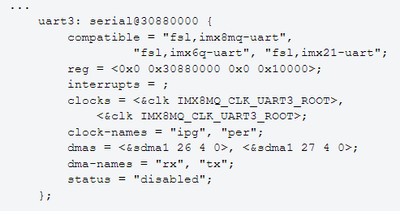

As for example in device tree here :

This is from this link :https://www.emcraft.com/som/imx-8m/using-imx-8m-uart-ports-in-linux

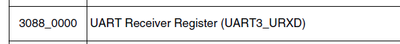

In the above tree I can directly map that UART3 address to the address in the UG, i.e

So.. why do I have my serials starting at 0x5a......... ?

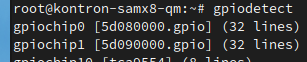

I have similar issue understanding what Linux's shows me for my GPIO ports:

Again, not addresses per my UG... Where does this come from, how to map to physical addresses to get actual physical peripheral ..?

If this is some standard device tree method to remap these, could you provide a link explaining how this works..?

已解决! 转到解答。

Hello,

This is actually the problem since you're not using an i.MX8M it is an i.MX8(QM), which is a different processor, sometimes the name causes confusion since it is really similar.

i.MX8(QM) processor webpage

https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-proces...

i.MX8(QM) Reference manual

https://www.nxp.com/webapp/Download?colCode=IMX8QMRM

Best regards,

Aldo.

I'm still lost on it, if you don't mind sending NXP's link to the document / User Guide you referring to?

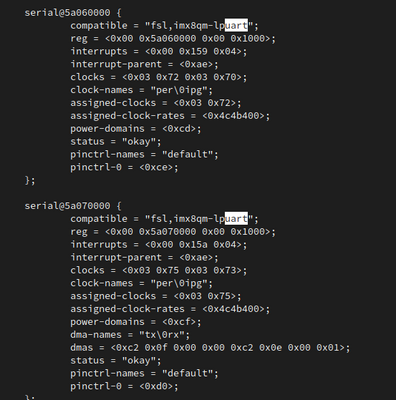

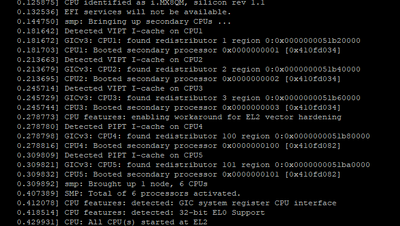

The first image is from the actual running system. Yes, it traces as having LPUART.

But the chip you have referred to i.MX8QM, if I check overview at NXP's site: https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-proces...

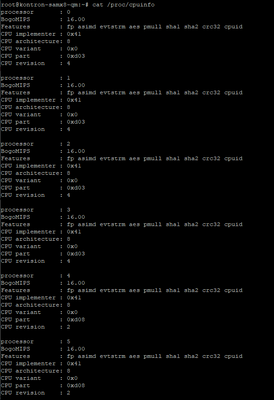

This has only one 4 core A53 complex, but my booted chip has 6 cores total managed by Linux, so I cannot find one QM variant with 6 cores - presumably A53 + A72 .. ?

Which iMX8 M then has 6 cores ?

Hello,

This is actually the problem since you're not using an i.MX8M it is an i.MX8(QM), which is a different processor, sometimes the name causes confusion since it is really similar.

i.MX8(QM) processor webpage

https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-proces...

i.MX8(QM) Reference manual

https://www.nxp.com/webapp/Download?colCode=IMX8QMRM

Best regards,

Aldo.

@AldoG Thank you, now its starting to look much better.

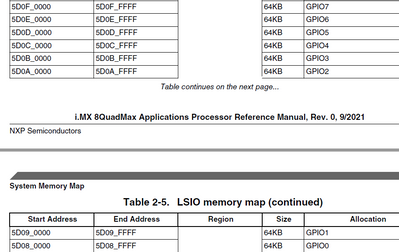

Is there similar one for the GPIO ones ..? I think I'm looking into Low Speed I/O sub-system but I cannot find a similar memory map for that sub-section for my I/O ...

Hello,

You have used an incorrect reference both for the reference manual and the example you have found.

From the first image you have shared it is from i.MX8QM and the reference you have used is the i.MX8MQ which is a different processor.

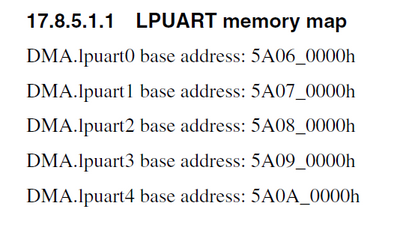

Following the first example, for the i.MX8QM LPUART is part of the DMA subsystem, from the i.MX8QM reference manual chapter 17.8.5.1.1 LPUART memory map:

DMA.lpuart0 base address: 5A06_0000h

DMA.lpuart1 base address: 5A07_0000h

As it is displayed in the device tree.

Best regards,

Aldo.