- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

PCIe link doesn't come up with XIO2001 PCI bridge on iMX6Q custom board

Hi All,

I'm trying to get a custom board, based on iMX6Q SoC, to bring up the PCIe link connected to a TI XIO2001 PCIe-to-PCI bridge.

I've apply some changes to a uboot v2014.04 so that the give XIO2001 is properly reset, the relevant code is the following:

static iomux_v3_cfg_t const pcie_pads[] = {

MX6_PAD_CSI0_DATA_EN__GPIO5_IO20 | MUX_PAD_CTRL(USDHC_PAD_CTRL), /* WAKE */

MX6_PAD_GPIO_9__GPIO1_IO09 | MUX_PAD_CTRL(NO_PAD_CTRL), /* PCIE_PWR_EN */

MX6_PAD_GPIO_16__GPIO7_IO11 | MUX_PAD_CTRL(NO_PAD_CTRL), /* GRST# */

MX6_PAD_GPIO_17__GPIO7_IO12 | MUX_PAD_CTRL(NO_PAD_CTRL), /* PERST# */

};

#define PCIE_XIO2001_GRST IMX_GPIO_NR(7, 11)

#define CONFIG_PCIE_IMX_PERST_GPIO IMX_GPIO_NR(7, 12)

#define CONFIG_PCIE_IMX_POWER_GPIO IMX_GPIO_NR(1, 9)

static void setup_iomux_pcie(void)

{

imx_iomux_v3_setup_multiple_pads(pcie_pads, ARRAY_SIZE(pcie_pads));

}

int imx6_pcie_toggle_power(void)

{

#ifdef CONFIG_PCIE_IMX_POWER_GPIO

/*

* TI XIO2001 Power Up procedure:

*

* 1) Assert both GRST# and PERST# without power voltages

*/

gpio_direction_output(CONFIG_PCIE_IMX_POWER_GPIO, 0);

gpio_direction_output(CONFIG_PCIE_IMX_PERST_GPIO, 0);

gpio_direction_output(PCIE_XIO2001_GRST, 0);

mdelay(10);

/*

* 2) Apply 1.5V and 3.3V voltages ... but maybe only 3.3V ;)!

*/

gpio_set_value(CONFIG_PCIE_IMX_POWER_GPIO, 1);

mdelay(10);

/*

* 3) Deassert GRST#

*/

gpio_set_value(PCIE_XIO2001_GRST, 1);

/*

* 4) After that we should apply a stable PCIe reference clock

* see drivers/pci/pcie_imx.c:imx6_pcie_deassert_core_reset()

*/

#endif

return 0;

}

int imx6_pcie_toggle_reset(void)

{

#ifdef CONFIG_PCIE_IMX_PERST_GPIO

/*

* 5) To meet PCIe specific requirements, PERST# cannot be deasserted util minimum 100ms

* after apply power and 100-us after apply stable reference clock.

*/

gpio_direction_output(CONFIG_PCIE_IMX_PERST_GPIO, 0);

mdelay(100);

gpio_set_value(CONFIG_PCIE_IMX_PERST_GPIO, 1);

#else

puts("WARNING: Make sure the PCIe #PERST line is connected!\n");

#endif

return 0;

}

This will end up on this uboot boot status:

U-Boot 2014.04-imx_v2014.04_3.14.28_1.0.0_ga+g88123ea (Feb 03 2016 - 10:56:45)

CPU: Freescale i.MX6Q rev1.5 at 792 MHz

CPU: Temperature 37 C, calibration data: 0x5624d569

Reset cause: POR

Board: Janas iMX6Q (ID:e315c0641d0f31d4)

I2C: ready

DRAM: 2 GiB

MMC: FSL_SDHC: 0, FSL_SDHC: 1

MMC Device 3 not found

No MMC card found

Using default environment

Starting XIO2001 power up sequence ...

Enabling PCIe reference clock ...

Deasserting PCIe PERST# ...

Deasserting PCIe PERST# ...

phy link never came up

DEBUG_R0: 0x00354800, DEBUG_R1: 0x08200000

In: serial

Out: serial

Err: serial

Found PFUZE100! deviceid=10,revid=21

Net: FEC [PRIME]

Warning: failed to set MAC address

=> pci

Scanning PCI devices on bus 0

BusDevFun VendorId DeviceId Device Class Sub-Class

_____________________________________________________________

pci_bus_to_hose() failed

pci_bus_to_hose() failed

pci_bus_to_hose() failed

pci_bus_to_hose() failed

booting up a yocto kernel linux-fslc 4.1 I'm getting this:

[ 0.537703] imx6q-pcie 1ffc000.pcie: phy link never came up

[ 0.538363] imx6q-pcie 1ffc000.pcie: PCI host bridge to bus 0000:00

[ 0.538385] pci_bus 0000:00: root bus resource [io 0x1000-0xffff]

[ 0.538403] pci_bus 0000:00: root bus resource [mem 0x01000000-0x01efffff]

[ 0.538422] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 0.539694] PCI: bus0: Fast back to back transfers disabled

[ 0.540036] PCI: bus1: Fast back to back transfers enabled

[ 0.540206] pci 0000:00:00.0: BAR 0: assigned [mem 0x01000000-0x010fffff]

[ 0.540234] pci 0000:00:00.0: BAR 6: assigned [mem 0x01100000-0x0110ffff pref]

[ 0.540254] pci 0000:00:00.0: PCI bridge to [bus 01]

[ 0.541065] pcieport 0000:00:00.0: Signaling PME through PCIe PME interrupt

root@voneus-janas-imx6q:~# lspci -vvv

00:00.0 PCI bridge: Synopsys, Inc. Device abcd (rev 01) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr+ Stepping- SERR+ FastB2B- DisINTx+

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 64 bytes

Interrupt: pin A routed to IRQ 290

Region 0: Memory at 01000000 (32-bit, non-prefetchable) [size=1M]

Bus: primary=00, secondary=01, subordinate=01, sec-latency=0

I/O behind bridge: 0000f000-00000fff

Memory behind bridge: fff00000-000fffff

Prefetchable memory behind bridge: fff00000-000fffff

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

[virtual] Expansion ROM at 01100000 [disabled] [size=64K]

BridgeCtl: Parity+ SERR- NoISA- VGA- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1+ D2- AuxCurrent=375mA PME(D0+,D1+,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst- PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [50] MSI: Enable+ Count=1/1 Maskable+ 64bit+

Address: 000000007d8b2000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [70] Express (v2) Root Port (Slot-), MSI 00

DevCap: MaxPayload 128 bytes, PhantFunc 0

ExtTag- RBE+

DevCtl: Report errors: Correctable+ Non-Fatal+ Fatal+ Unsupported+

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop-

MaxPayload 128 bytes, MaxReadReq 512 bytes

DevSta: CorrErr- UncorrErr- FatalErr- UnsuppReq- AuxPwr+ TransPend-

LnkCap: Port #0, Speed 2.5GT/s, Width x1, ASPM L0s L1, Exit Latency L0s <1us, L1 <8us

ClockPM- Surprise- LLActRep+ BwNot- ASPMOptComp-

LnkCtl: ASPM Disabled; RCB 64 bytes Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s, Width x1, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

RootCtl: ErrCorrectable- ErrNon-Fatal- ErrFatal- PMEIntEna+ CRSVisible-

RootCap: CRSVisible-

RootSta: PME ReqID 0000, PMEStatus- PMEPending-

DevCap2: Completion Timeout: Range ABCD, TimeoutDis+, LTR-, OBFF Not Supported ARIFwd-

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled ARIFwd-

LnkCtl2: Target Link Speed: 5GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete-, EqualizationPhase1-

EqualizationPhase2-, EqualizationPhase3-, LinkEqualizationRequest-

Capabilities: [100 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr-

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr+

AERCap: First Error Pointer: 00, GenCap+ CGenEn- ChkCap+ ChkEn-

Capabilities: [140 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=1

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=00 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64- WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=Fixed TC/VC=ff

Status: NegoPending+ InProgress-

Kernel driver in use: pcieport

Do you have any suggestion how to solve this?

Thanks in advance,

Roberto Fichera.

You can try to force Gen1 mode and see if it helps.

Also, please take a look at this patch from Tim Harvey:

[PATCH v2] PCI: imx6: add dt prop for link gen, default to gen1 — Linux PCI

Are you able to try this PCI device on a NXP reference board?

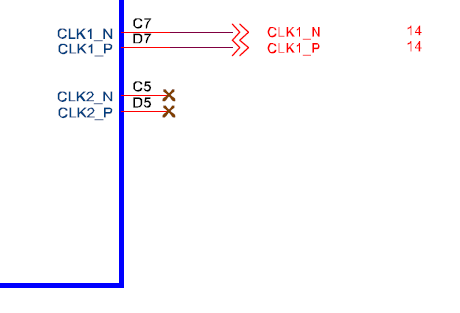

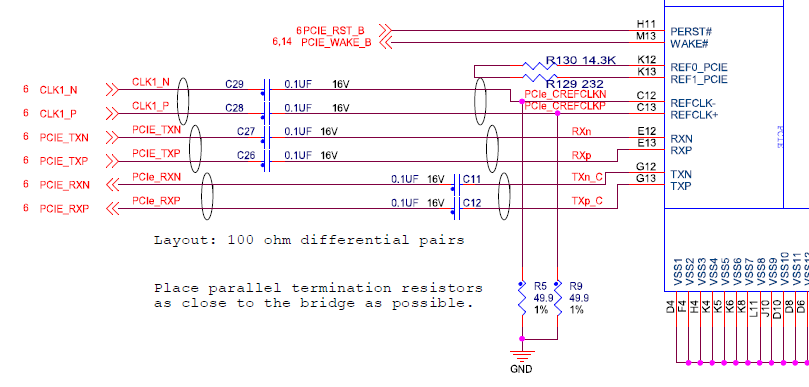

I would just add some additional info. The PCB is similar to Sabresd AI board, it uses CLK1_N/P pads as clock source for the TI XIO2001 PCIe-to-PCI bridge but we don't use any external oscillator, so this means we are only PCIe Gen1 speed compliance

Hi Roberto,

in your schematics are C's for PCIE_RX* . However, when you compare to sabre AI rev D, sabre SDB C4, or sabre SDP C4, you will find 0 Ohm resistors. We had "phy link never came up" until we removed the PCIE_RX* C's for a tw6869 PCIe chip.

hth

Frank

Hi Frank,

we have also tried to remove the C's from PCIE_RX* even if this is not really PCIe compliance as reported by our HW engineer, because these Freescale boards all use a PCIe slot and therefore the RX has a capacitor on the add-in board (PCIe standard).

Since we don't have a slot, PCIe is connected straight to the TI XIO2001 bridge, we have capacitors on RX and TX on the PCB. So we are PCIe compliant. We tested just in case of bugs here. Unfortunately doesn't change current status, PCIe goes in L0 in uboot but as soon as the kernel starts, PCIe reaches S_POLL_COMPLIANCE and never progress from this state:

[ 0.237985] imx6q-pcie 1ffc000.pcie: Looks like PCIe link was already enabled by bootloader

[ 0.347961] imx6q-pcie 1ffc000.pcie: >>> GPR[1]: 0x48611005

[ 0.347979] imx6q-pcie 1ffc000.pcie: >>> GPR[8]: 0xfffd4000

[ 0.347996] imx6q-pcie 1ffc000.pcie: >>> GPR[12]: 0x0f004090

[ 0.348012] imx6q-pcie 1ffc000.pcie: >>> ANA_MISC1: 0x8000040b

[ 0.348027] imx6q-pcie 1ffc000.pcie: >>> PLL_ENET: 0x80182001

[ 0.348042] imx6q-pcie 1ffc000.pcie: >>> CCM_CCGR4 (0xf0948078): 0x00fff303

[ 0.348056] imx6q-pcie 1ffc000.pcie: >>> CCM_CCGR5 (0xf094807c): 0x0f0000f3

[ 0.348068] imx6q-pcie 1ffc000.pcie: >>> PCIE_RC_LCR (0xf08f007c): 0x0011cc11

[ 0.348086] imx6q-pcie 1ffc000.pcie: ----- After Starting LTSSM and wait_for_link() -----

[ 0.348102] imx6q-pcie 1ffc000.pcie: GPIO PCIE_PWR status : 1

[ 0.348117] imx6q-pcie 1ffc000.pcie: GPIO PCIE_GRST status : 1

[ 0.348132] imx6q-pcie 1ffc000.pcie: GPIO PCIE_PERST status: 1

[ 0.348146] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x0 (S_DETECT_QUIET)

[ 0.348157] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 0.367864] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x2 (S_POLL_ACTIVE)

[ 0.367880] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 0.387852] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 0.387866] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 0.407853] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 0.407869] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 0.427850] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 0.427866] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 0.447852] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

...

[ 4.247864] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 4.267851] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 4.267865] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 4.287852] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 4.287866] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 4.307850] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 4.307864] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 4.327849] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 4.327864] imx6q-pcie 1ffc000.pcie: LINK-UP or NOT in TRAINING

[ 4.347849] imx6q-pcie 1ffc000.pcie: phy link never came up

[ 4.347866] imx6q-pcie 1ffc000.pcie: ----- Last LTSSM Status -----

[ 4.347882] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x3 (S_POLL_COMPLIANCE)

[ 4.347893] imx6q-pcie 1ffc000.pcie: PIPE transmit K indication: 1

[ 4.347906] imx6q-pcie 1ffc000.pcie: PIPE Transmit data: 0x4abc

[ 4.347920] imx6q-pcie 1ffc000.pcie: Receiver is receiving logical idle: no

[ 4.347931] imx6q-pcie 1ffc000.pcie: Second symbol is also idle (16-bit PHY interface only): no

[ 4.347943] imx6q-pcie 1ffc000.pcie: Currently receiving k237 (PAD) in place of link number: no

[ 4.347955] imx6q-pcie 1ffc000.pcie: Currently receiving k237 (PAD) in place of lane number: no

[ 4.347967] imx6q-pcie 1ffc000.pcie: Link control bits advertised by link partner: 0x0

[ 4.347979] imx6q-pcie 1ffc000.pcie: Receiver detected lane reversal: no

[ 4.347990] imx6q-pcie 1ffc000.pcie: TS2 training sequence received: no

[ 4.348001] imx6q-pcie 1ffc000.pcie: TS1 training sequence received: no

[ 4.348011] imx6q-pcie 1ffc000.pcie: Receiver reports skip reception: no

[ 4.348022] imx6q-pcie 1ffc000.pcie: LTSSM reports PHY link up: no

[ 4.348033] imx6q-pcie 1ffc000.pcie: A skip ordered set has been transmitted: no

[ 4.348045] imx6q-pcie 1ffc000.pcie: Link number advertised/confirmed by link partner: 0

[ 4.348055] imx6q-pcie 1ffc000.pcie: Application request to initiate training reset: no

[ 4.348066] imx6q-pcie 1ffc000.pcie: PIPE transmit compliance request: no

[ 4.348077] imx6q-pcie 1ffc000.pcie: PIPE transmit electrical idle request: no

[ 4.348088] imx6q-pcie 1ffc000.pcie: PIPE receiver detect/loopback request: no

[ 4.348099] imx6q-pcie 1ffc000.pcie: LTSSM-negotiated link reset: yes

[ 4.348110] imx6q-pcie 1ffc000.pcie: LTSSM testing for polarity reversal: no

[ 4.348120] imx6q-pcie 1ffc000.pcie: LTSSM performing link training: no

[ 4.348131] imx6q-pcie 1ffc000.pcie: LTSSM in DISABLE state; link inoperable: no

[ 4.348142] imx6q-pcie 1ffc000.pcie: Scrambling disabled for the link: no

[ 4.348154] imx6q-pcie 1ffc000.pcie: ----------------------------------------------------

Roberto,

Our design that has a XIO2001 bridge directly to an IMX6 has 0.1uF caps on both TX and RX signals (all four signals) and we do not connect WAKE# (pin left floating). If you are getting a PCI link in U-Boot but not the kernel then I bet you are having an issue with PCI_RST#. Are you certain you have that signal setup correctly in the device-tree and you see it asserted low for 100ms during the kernel drivers PCI init?

We have had many issues when enabling PCI in Uboot 'and' the kernel due to the fact that the IMX6 PCIe host has no proper reset so we always leave it disabled in Uboot. We have also found that depending on what kernel we are using we have needed various patches in the PCIe host controller driver to deal with the lack of reset and differences in timing. I'm not sure what kernel your using but we do have a patch in our 3.14 kernel tree that resolved PCI link failures in certain circumstances: pci: imx6: Add delay after LTSSM transition · Gateworks/linux-imx6@89a86a8 · GitHub

We also have a patch that disables Gen2 that you may want to try pci: imx6: disable Gen2 · Gateworks/linux-imx6@9ed858f · GitHub

Regards,

Tim

Hi Tim,

I've solved the problem yesterday by asserting PERST before to drop PCIe refclk and TEST_POWER_DOWN in the kernel driver. PERST deassert is happening at the usual place. DTS is using 2 fixed regulators to keep PWR_EN and GRST pins as they are coming from uBoot.

I've also applied a slightly modified disable Gen2 patch and added a 10us delay when enabling reflck and disabling TEST_POWER_DOWN.

Cheers,

Roberto Fichera.

We are also working in custom board, based on iMX7D SoC, to bring up the PCIe link connected to a TI TUSB7320IRKMT PCIe-to-USB bridge. We too facing the issue of phy link never came up.

log:

[ 0.354326] PCI: CLS 0 bytes, default 64

[ 0.536259] OF: PCI: host bridge /soc/pcie@0x33800000 ranges:

[ 0.536279] OF: PCI: No bus range found for /soc/pcie@0x33800000, using [bus 00-ff]

[ 0.536303] OF: PCI: IO 0x4ff80000..0x4ff8ffff -> 0x00000000

[ 0.536321] OF: PCI: MEM 0x40000000..0x4fefffff -> 0x40000000

[ 0.781821] imx6q-pcie 33800000.pcie: phy link never came up

[ 0.781834] imx6q-pcie 33800000.pcie: Link never came up

[ 0.784951] imx6q-pcie 33800000.pcie: failed to initialize host

[ 0.785150] imx6q-pcie: probe of 33800000.pcie failed with error -110

[ 1.860571] ehci-pci: EHCI PCI platform driver

The uboot support for PCI in iMX7 is not yet implemented. So we couldn't test the PCI in uboot level.

But the power up sequences of your PCI bridge seems similar to our PCI USB controller chip.

Can you please share us the the changes you have done in the PCI host controller driver and configurations enabled in kernel in detail?

Thanks,

Koil Arul Raj.S

Roberto,

You are missing the proper conversion from the IMX6 LVDS CLK output to the HSCL level clock the TI bridge requires. Take a look at the latest Freescale reference designs and you will see pull-ups and pull-downs on the 'device side' (bridge side in your case) to properly DC bias the clock for an HSCL level which PCIe uses. For LVDS->HSCL after the AC coupling capacitor you would want 470ohm pull-ups to 3.3V and 56ohm pull-downs to GND which will give you the proper HSCL DC level.

Regards,

Tim

Hi Tim,

our HW engineer has applied the changes you notice. However I'm still getting the same problem. I've tried to boot a kernel with an uboot not setting up the PCIe subsys and below there is the resulting kernel log. Note that the CCGR5 doesn't set the CG2 field associated to sata_clk_enable. I think this field should be set all 1 to enable the SATA ref at 100MHz, right?

[ 0.237052] PCI host bridge /soc/pcie@0x01000000 ranges:

[ 0.237070] No bus range found for /soc/pcie@0x01000000, using [bus 00-ff]

[ 0.237119] err 0x01f00000..0x01f7ffff -> 0x01f00000

[ 0.237157] IO 0x01f80000..0x01f8ffff -> 0x00000000

[ 0.237241] MEM 0x01000000..0x01efffff -> 0x01000000

[ 0.437893] imx6q-pcie 1ffc000.pcie: >>> GPR[1]: 0x48611005

[ 0.437913] imx6q-pcie 1ffc000.pcie: >>> GPR[8]: 0xfffd4000

[ 0.437927] imx6q-pcie 1ffc000.pcie: >>> GPR[12]: 0x0f004000

[ 0.437945] imx6q-pcie 1ffc000.pcie: >>> ANA_MISC1: 0x8000040b

[ 0.437959] imx6q-pcie 1ffc000.pcie: >>> PLL_ENET: 0x80182001

[ 0.437973] imx6q-pcie 1ffc000.pcie: >>> CCM_CCGR4 (0xf08f8078): 0x00fff303

[ 0.437989] imx6q-pcie 1ffc000.pcie: >>> CCM_CCGR5 (0xf08f807c): 0x0f0000c3

[ 0.438003] imx6q-pcie 1ffc000.pcie: >>> PCIE_RC_LCR (0xf08f007c): 0x0011cc11

[ 4.437756] imx6q-pcie 1ffc000.pcie: phy link never came up

[ 4.437774] imx6q-pcie 1ffc000.pcie: LTSSM current state: 0x2 (S_POLL_ACTIVE)

[ 4.437786] imx6q-pcie 1ffc000.pcie: PIPE transmit K indication: 0

[ 4.437799] imx6q-pcie 1ffc000.pcie: PIPE Transmit data: 0x4a4a

[ 4.437811] imx6q-pcie 1ffc000.pcie: Receiver is receiving logical idle: no

[ 4.437824] imx6q-pcie 1ffc000.pcie: Second symbol is also idle (16-bit PHY interface only): no

[ 4.437837] imx6q-pcie 1ffc000.pcie: Currently receiving k237 (PAD) in place of link number: no

[ 4.437849] imx6q-pcie 1ffc000.pcie: Currently receiving k237 (PAD) in place of lane number: no

[ 4.437862] imx6q-pcie 1ffc000.pcie: Link control bits advertised by link partner: 0x0

[ 4.437873] imx6q-pcie 1ffc000.pcie: Receiver detected lane reversal: no

[ 4.437883] imx6q-pcie 1ffc000.pcie: TS2 training sequence received: no

[ 4.437894] imx6q-pcie 1ffc000.pcie: TS1 training sequence received: no

[ 4.437905] imx6q-pcie 1ffc000.pcie: Receiver reports skip reception: no

[ 4.437915] imx6q-pcie 1ffc000.pcie: LTSSM reports PHY link up: no

[ 4.437926] imx6q-pcie 1ffc000.pcie: A skip ordered set has been transmitted: no

[ 4.437939] imx6q-pcie 1ffc000.pcie: Link number advertised/confirmed by link partner: 0

[ 4.437951] imx6q-pcie 1ffc000.pcie: Application request to initiate training reset: no

[ 4.437963] imx6q-pcie 1ffc000.pcie: PIPE transmit compliance request: no

[ 4.437975] imx6q-pcie 1ffc000.pcie: PIPE transmit electrical idle request: no

[ 4.437985] imx6q-pcie 1ffc000.pcie: PIPE receiver detect/loopback request: no

[ 4.437996] imx6q-pcie 1ffc000.pcie: LTSSM-negotiated link reset: yes

[ 4.438006] imx6q-pcie 1ffc000.pcie: LTSSM testing for polarity reversal: no

[ 4.438017] imx6q-pcie 1ffc000.pcie: LTSSM performing link training: no

[ 4.438028] imx6q-pcie 1ffc000.pcie: LTSSM in DISABLE state; link inoperable: no

[ 4.438038] imx6q-pcie 1ffc000.pcie: Scrambling disabled for the link: no

[ 4.438620] imx6q-pcie 1ffc000.pcie: PCI host bridge to bus 0000:00

[ 4.438644] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 4.438662] pci_bus 0000:00: root bus resource [??? 0x01f00000-0x01f7ffff flags 0x0]

[ 4.438678] pci_bus 0000:00: root bus resource [io 0x0000-0xffff]

[ 4.438693] pci_bus 0000:00: root bus resource [mem 0x01000000-0x01efffff]

[ 4.438812] pci 0000:00:00.0: [16c3:abcd] type 01 class 0x060400

[ 4.438875] pci 0000:00:00.0: reg 0x10: [mem 0x00000000-0x000fffff]

[ 4.438914] pci 0000:00:00.0: reg 0x38: [mem 0x00000000-0x0000ffff pref]

[ 4.439101] pci 0000:00:00.0: supports D1

[ 4.439119] pci 0000:00:00.0: PME# supported from D0 D1 D3hot D3cold

[ 4.439867] PCI: bus0: Fast back to back transfers disabled

[ 4.440202] PCI: bus1: Fast back to back transfers enabled

[ 4.440365] pci 0000:00:00.0: BAR 0: assigned [mem 0x01000000-0x010fffff]

[ 4.440394] pci 0000:00:00.0: BAR 6: assigned [mem 0x01100000-0x0110ffff pref]

[ 4.440413] pci 0000:00:00.0: PCI bridge to [bus 01]

[ 4.441193] pcieport 0000:00:00.0: Signaling PME through PCIe PME interrupt

[ 4.441222] pcie_pme 0000:00:00.0:pcie01: service driver pcie_pme loaded

[ 4.441618] aer 0000:00:00.0:pcie02: service driver aer loaded

Hi Roberto

one try to narrow down problem if this is caused by hardware,

attaching some other pcie module or use this bridge on sabre board.

Some useful links:

git.denx.de Git - u-boot.git/commitdiff

How to setup i.MX6Dual/Quad and i.MX6Solo/DualLite Linux software for PCIe compliance Test?

Also suggest you that make sure to clear MX6 ltssm_en before refclock stable, and

assert it after release “PCIE_A_RST#” to the PCIe module, so that to make both side detect simultaneously.

20ms delay is required after the PERST is de-asserted during the iMX PCIe RC driver initialization.

Just like the following example:

/* Some boards don't have PCIe reset GPIO. */

if (gpio_is_valid(imx6_pcie->reset_gpio)) {

gpio_set_value_cansleep(imx6_pcie->reset_gpio, 0);

mdelay(100);

gpio_set_value_cansleep(imx6_pcie->reset_gpio, 1);

/*

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

unfortunately this is a custom board so I cannot easily replace the PCIe-to-PCI bridge. Regarding the rest of your answer, I've applied the patch you suggested related to enable REF_SSP_EN after 50ms of delay to my uboot-imx 2014.04. But still the same problem.

Cheers,

Roberto Fichera.

I did some progress here, currently uboot is able to detect the devices in the PCIe bus, but the kernel fslc v4.4 still reporting the phy link never came up.

Any idea how to fix it?

Cheers,

Roberto Fichera.

U-Boot 2014.04-imx_v2014.04_3.14.38_6qp_beta+g6e9282c (Feb 15 2016 - 10:02:31)

CPU: Freescale i.MX6Q rev1.5 at 792 MHz

CPU: Temperature 35 C, calibration data: 0x5664d569

Reset cause: POR

Board: Janas iMX6Q (ID:e315c064140749d4)

I2C: ready

DRAM: 2 GiB

MMC: FSL_SDHC: 0, FSL_SDHC: 1

*** Warning - bad CRC, using default environment

00:01.0 - 16c3:abcd - Bridge device

01:00.0 - 104c:8240 - Bridge device

02:04.0 - 1397:08b4 - Network controller

In: serial

Out: serial

Err: serial

Found PFUZE100! deviceid=10,revid=21

mmc1(part 0) is current device

Net: FEC [PRIME]

Warning: failed to set MAC address

Normal Boot

....

....

[ 0.236141] PCI host bridge /soc/pcie@0x01000000 ranges:

[ 0.236162] No bus range found for /soc/pcie@0x01000000, using [bus 00-ff]

[ 0.236213] err 0x01f00000..0x01f7ffff -> 0x01f00000

[ 0.236250] IO 0x01f80000..0x01f8ffff -> 0x00000000

[ 0.236330] MEM 0x01000000..0x01efffff -> 0x01000000

[ 0.546690] imx6q-pcie 1ffc000.pcie: phy link never came up

[ 0.547263] imx6q-pcie 1ffc000.pcie: PCI host bridge to bus 0000:00

[ 0.547287] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 0.547304] pci_bus 0000:00: root bus resource [??? 0x01f00000-0x01f7ffff flags 0x0]

[ 0.547321] pci_bus 0000:00: root bus resource [io 0x0000-0xffff]

[ 0.547335] pci_bus 0000:00: root bus resource [mem 0x01000000-0x01efffff]

[ 0.548608] PCI: bus0: Fast back to back transfers disabled

[ 0.548950] PCI: bus1: Fast back to back transfers enabled

[ 0.549107] pci 0000:00:00.0: BAR 0: assigned [mem 0x01000000-0x010fffff]

[ 0.549137] pci 0000:00:00.0: BAR 6: assigned [mem 0x01100000-0x0110ffff pref]

[ 0.549159] pci 0000:00:00.0: PCI bridge to [bus 01]

[ 0.549945] pcieport 0000:00:00.0: Signaling PME through PCIe PME interrupt

...

Have you added a regulator controlled by gpio1_9 in your dts?

In imx6qdl-sabresd.dtsi we have the reg_pcie regulator.