- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

LVDS panel display corruption

Hi,

We are using custom hardware based on IMX6q.

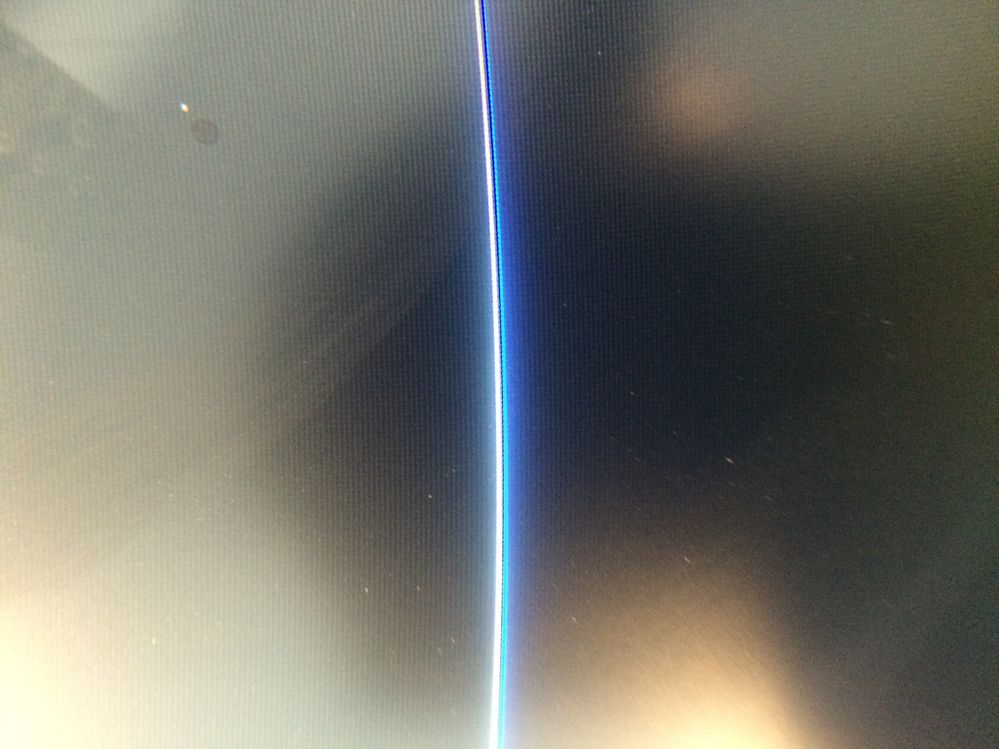

LVDS panel is connected to hardware and some times we are getting display corruption.

How we can fixed this issue? What could be the reason behind this?

Thanks

Saurabh

Hi,

Any Valuable guideline from Freescale Team?

Thanks

Saurabh

I would said that the issue it is timing related, you can review the fb structure that it is according to your LVDS display. I would recommend to measure the pixel clock to see it is according to the LVDS. Can you share your settings? Another way to review it is to slow down the resolution of the display to see if it is corrected.

Have a great day,

Jaime

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi,

Thanks for taking interest and replay for this issue.

This issue occurs randomly. After reboot or suspend resume this issue disappear and visa verse.

I am using 1080p display Panel.

static struct fb_videomode ldb_modedb[] = {

"LDB-1080P60", 60, 1920, 1080, 6800,

128, 138 ,

22, 3,

80, 4,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

};

And pll2_pfd_352M is used as clocking source for the LDB pixel clock,

Is It possible LDB pixel clock (pll2_pfd_352M ) has some jitter ?

Thanks

Saurabh

Hi,

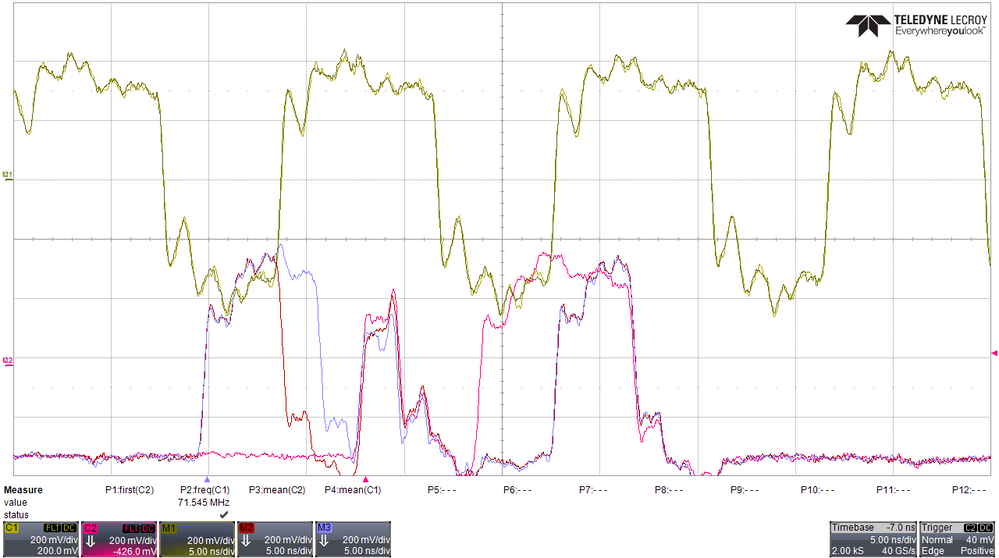

I have measured the clock signal

- LVDS0_CLK_P signal and it is always vary between 69.9 MHz to 73.3 MHz.

According to me it should be stable at any one value according to rounding clock rate. What could be wrong in this case?

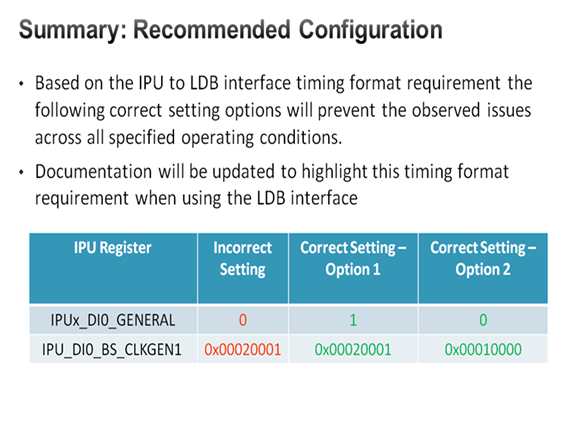

In LDB split mode how the LVDS0_CLK_P and LVDS1_CLK_P generated from IPU_DI0_CLK?

When i have display corruption difference between LVDS0_CLK_P and LVDS1_CLK_P is approx 2 Hz, And for the proper picture this difference is between 0.2 Hz.

- Ideally this both clock LVDS0_CLK_P and LVDS1_CLK_P should be same because it is generated from same clock source.

Any Valuable comment from Freescale team?

Saurabh

Hi Rod,

I have the same issue and i have solved it with your settings. Thank you. I would like to give some more information about what i saw. First i made a .bmp picture with only one pixel RGB colour = 127, 127 and 127. Then I send the whole picture to the screen using the following linux command:

dd if=/media/sda1/test.bmp bs=138 skip=1 > /dev/fb (The test image is a 1280x800 RGB565 bitmap file)

We then saw a shift in pixels:

When setting the following setting: addr 0x02640008 to 0x00020001 (was 0x00010000), the problem was fixed.

Below a measurement of the LVDS signals, CLK and RX1:

Red and blue are the incorrect image with shifted bits. Pink is the correct image.

Hello, Thank you for sharing you info, I got somehow similar problem. Could you guys kindly share with me how to set or read the register values for imx6? How do we check and change the value of the following registers?

IPU_DI0_GENERAL

IPU_DI0_BS_CLKGEN0

IPU_DI0_BS_CLKGEN1

Thank s a lot

Hi,

Rod

Register values are as follow.

IPU_DI0_GENERAL --> 0x00300000;

IPU_DI0_BS_CLKGEN0 --> 0x00000010;

IPU_DI0_BS_CLKGEN1 --> 0x00010000;

Regards

Saurabh

I was able to patch the 3.10.17 GA FSL kernel (using the code above) and the LVDS is now working without issue. We are still testing but all looks good. It appears I can not attach files to this post so I'm not sure how I can post the patch.

Thanks,

Jeff

Hi,

Rod

I have applied the patch and there a improvement.

I will test for longer period of time and provide you update.

Thanks

Saurabh