- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: IPU2 CS1 1080p60 YUY2 16-bit capture over i.MX6QDL

IPU2 CS1 1080p60 YUY2 16-bit capture over i.MX6QDL

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IPU2 CS1 1080p60 YUY2 16-bit capture over i.MX6QDL

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

We already designed a product using iMX6 Dual / Quad and this one is able to capture 1080p30 HDMI video using an ADV7612. Parallel bus from ADV7612 is sent to IPU1_CSI0 of iMX6. ADV7612 is working DDR (PIXCLK at 2 x 74.25MHz) with 8-bit pixel bus @ 1080p30.

We are using a Variscite VAR-SOM-MX6 and we would like to be able to do 1080p60 using same module.

We have found that Variscite VAR-SOM-MX6 exposes 20-bit CSI port of IPU2_CSI1 compared to IPU1_CS0 which exposes only 12-bits. We cannot do 1080p60 with that interface. We would like to be able to put the ADV7612 parallel port 16-bit (8-bit luma and 8-bit chroma) with PIXCLK at 148.5MHz for 1080p60.

Is it achievable with iMX6 Quad / Dual? Seems like in the datasheet CSI parallel can work up to 240MHz.

We base our driver for ADV7612 on the ov564x driver.

I am trying to modify the imx6q-var-som-vsc.dts file by adding this:

&i2c1 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c1_2>;

status = "okay";

ov564x: ov564x@3c {

compatible = "ovti,ov564x";

reg = <0x3c>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ipu1_2>;

clocks = <&clks IMX6QDL_CLK_CKO>;

clock-names = "csi_mclk";

//DOVDD-supply = <&vgen4_reg>; /* 1.8v */

//AVDD-supply = <&vgen3_reg>; /* 2.8v, on rev C board is VGEN3,

// on rev B board is VGEN5 */

//DVDD-supply = <&vgen2_reg>; /* 1.5v*/

//pwn-gpios = <&gpio1 16 1>; /* active low: SD1_DAT0 */

//rst-gpios = <&gpio1 17 0>; /* active high: SD1_DAT1 */

csi_id = <1>;

mclk = <24000000>;

mclk_source = <0>;

};

};

We also add this pin-ctrl to iomuxc

pinctrl_ipu1_2: ipu1grp-2 { /* parallel camera */

fsl,pins = <

MX6QDL_PAD_EIM_DA9__IPU2_CSI1_DATA00 0x10000

MX6QDL_PAD_EIM_DA8__IPU2_CSI1_DATA01 0x10000

MX6QDL_PAD_EIM_DA7__IPU2_CSI1_DATA02 0xb0b1

MX6QDL_PAD_EIM_DA6__IPU2_CSI1_DATA03 0xb0b1

MX6QDL_PAD_EIM_DA5__IPU2_CSI1_DATA04 0xb0b1

MX6QDL_PAD_EIM_DA4__IPU2_CSI1_DATA05 0xb0b1

MX6QDL_PAD_EIM_DA3__IPU2_CSI1_DATA06 0xb0b1

MX6QDL_PAD_EIM_DA2__IPU2_CSI1_DATA07 0xb0b1

MX6QDL_PAD_EIM_DA1__IPU2_CSI1_DATA08 0xb0b1

MX6QDL_PAD_EIM_DA0__IPU2_CSI1_DATA09 0xb0b1

MX6QDL_PAD_EIM_EB1__IPU2_CSI1_DATA10 0x10000

MX6QDL_PAD_EIM_EB0__IPU2_CSI1_DATA11 0x10000

MX6QDL_PAD_EIM_A17__IPU2_CSI1_DATA12 0xb0b1

MX6QDL_PAD_EIM_A18__IPU2_CSI1_DATA13 0xb0b1

MX6QDL_PAD_EIM_A19__IPU2_CSI1_DATA14 0xb0b1

MX6QDL_PAD_EIM_A20__IPU2_CSI1_DATA15 0xb0b1

MX6QDL_PAD_EIM_A21__IPU2_CSI1_DATA16 0xb0b1

MX6QDL_PAD_EIM_A22__IPU2_CSI1_DATA17 0xb0b1

MX6QDL_PAD_EIM_A23__IPU2_CSI1_DATA18 0xb0b1

MX6QDL_PAD_EIM_A24__IPU2_CSI1_DATA19 0xb0b1

MX6QDL_PAD_EIM_DA10__IPU2_CSI1_DATA_EN 0xb0b1

MX6QDL_PAD_EIM_DA11__IPU2_CSI1_HSYNC 0x10000

MX6QDL_PAD_EIM_DA12__IPU2_CSI1_VSYNC 0x10000

MX6QDL_PAD_EIM_A16__IPU2_CSI1_PIXCLK 0xb0b1

>;

};

In the imx6qdl-var-som.dtsi file, we changed this node:

v4l2_cap_0 {

compatible = "fsl,imx6q-v4l2-capture";

ipu_id = <1>;

csi_id = <1>;

mclk_source = <0>;

status = "okay";

};

When booting our Linux, here is what we get when doing dmesg | grep ov:

[ 0.119680] cpuidle: using governor ladder

[ 0.149678] cpuidle: using governor menu

[ 3.240495] sit: IPv6 over IPv4 tunneling driver

[ 3.834873] EXT4-fs (mmcblk1p2): recovery complete

[ 4.938636] ov564x 0-003c: Error applying setting, reverse things back

[ 4.944876] ov5640_probe

[ 5.052599] ov564x 0-003c: Error applying setting, reverse things back

[ 5.072072] ov564x 0-003c: set io voltage ok

[ 5.085775] ov564x 0-003c: set core voltage ok

[ 5.090943] ov564x 0-003c: set analog voltage ok

[ 5.203270] camera ov5640 is found

[ 5.953170] ov5640: unsupported bit mode 0

[ 5.969493] EXT4-fs (mmcblk0p1): recovery complete

How do we successfully change IPU_ID and CSI_ID in kernel in order to use the IPU2_CSI1 interface?

Thanks,

Jérôme

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

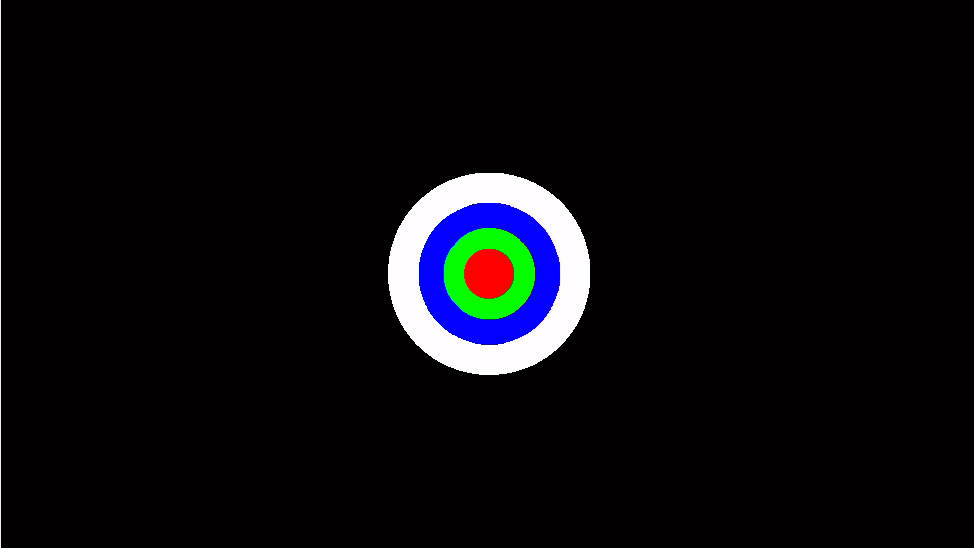

I should be able to capture YUV 1920x1080p 60fps image like this one:

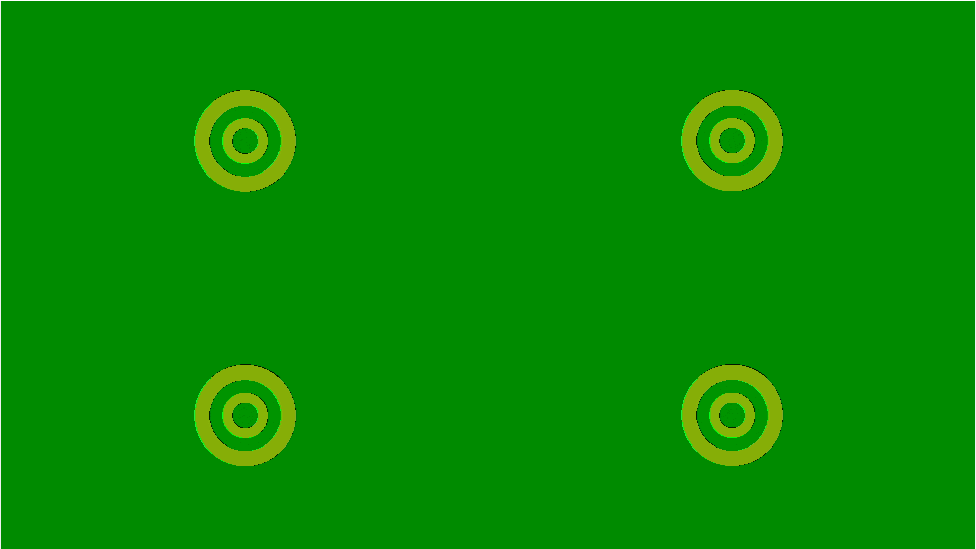

However, I am capturing something like this:

The video feed goes from top to bottom on constant speed without stablizing.

REG 0x2a38000 = 0x0400cb00

Seems like chroma is seen like luma.

In ipu_capture.c, I need to set this in order to capture 16-bit.

cfg_param.data_fmt = CSI_SENS_CONF_DATA_FMT_BAYER;

How to tell the IPU that incoming data is YUV?

Thanks!

Jerome

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

did you try the patch or not? still get the error with this patch?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

you should connect ADV7612 to mipi csi, right? refer to the reference manual,

The maximum bandwidth of the interface is as follows:

• 200Mhz for 4 data lanes configuration (800Mbps/lane, 400MByte/sec)

• 187.5Mhz for 3 data lanes configuration (1000Mbps/lane, 375MByte/sec)

• 125Mhz for 2 data lanes configuration (1000Mbps/lane, 250MByte/sec )

• 62.5Mhz for 1 data lane configuration (1000Mbps/lane, 125Mbyte/sec)

and if you use RGB565 over 16 bit format, I think you need to enable 4 data lans for this, for 16bits capture, you can refer to the enclosed patch for reference

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

ADV7612 output is parallel, not MIPI-CSI.

How to enable 16-bit YUY2 parallel capture on kernel?

Jérôme

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

refer to the data sheet, YCbCr, 16 bits—Supported as a “generic-data” input, I send the patch to you for 16bits generic data capture, you can refe to it,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This patch is already applied to our BSP.

I configured kernel to capture IPU_PIX_FMT_GENERIC_16.

How to tell iMX6 this generic capture is YUYV? Pixel mapping is not correct right now.

Regards,

Jérôme

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any updates on this?