- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: I.MX RT FlexSPI hyperram determining LUT operands

I.MX RT FlexSPI hyperram determining LUT operands

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.MX RT FlexSPI hyperram determining LUT operands

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to understand how to determine the LUT operands such as the number of dummy cycles to use for a hyperram device. I have opened a thread about the somewhat older example included in AN12239 here: https://community.nxp.com/t5/i-MX-Processors/Flexspi-hyperram-example-no-longer-included-in-i-MX-RT-...

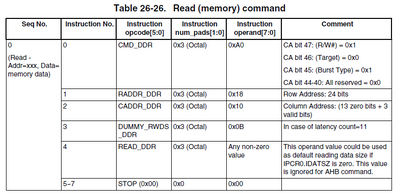

I'm running the code on a custom board using an I.MXRT1064, but luckily, I'm also using Cypress S27KL series. I had some trouble finding out how the lookup table is constructed, because the hyperbus spec. is very abstract and there seems to be very little correlation between the timing diagrams in the datasheet and the entries in the LUT. I was finally able to find an explanation in the reference manual through tables 26-26 and 26-29.

Now the meaning of the operands is clear to me, although again it is quite difficult to see how they relate to the datasheet values.

For example, I am not sure how the number of dummy cycles can be determined other than through trial and error. I'm assuming the number of dummy cycles depends on the selected clock frequency, supply voltage and of course the specific device. In the AN12239 example, a value of 0x06 is used. The reference manual uses a value of 0x0B and mentions "in case of latency count 11". I see that my data is basically "shifted" in the read register when the memcmp(s_hyper_ram_read_buffer, s_hyper_ram_write_buffer, ...) is executed. I was able to get a match when changing the number of dummy cycles to 0x07, but I'd like to understand a bit better how to determine this value based on the datasheet.

Other than the number of dummy cycles, there are some operands such as RADDR_DDR=0x18, CADDR_DDR=0x10 and READ_DDR=0x04 that seem somewhat arbitrary. Maybe it's obvious when you know it, but I could not figure out based on the datasheet why these specific values are used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

Firstly, the LUT for the Hyperbus protocol is actually a bit abstract,

next, it should be called a latency count instead of a dummy cycle, the above table is actually for the Hyperflash, not the HyperRAM.

In a word, I was wondering if you can illustrate which exactly LUT command you want to adjust.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

Thanks for your response.

I do not want to change any particular command if it's not necessary. Rather, I'd like to understand the LUT a bit better to make sure it's optimal for my application and make sure there is no unintended behavior. When I look at a LUT entry such as the following:

/* Write Data */

[4 * HYPERRAM_CMD_LUT_SEQ_IDX_WRITEDATA] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_DDR, kFLEXSPI_8PAD, 0x20, kFLEXSPI_Command_RADDR_DDR, kFLEXSPI_8PAD, 0x18),

[4 * HYPERRAM_CMD_LUT_SEQ_IDX_WRITEDATA + 1] = FLEXSPI_LUT_SEQ(

kFLEXSPI_Command_CADDR_DDR, kFLEXSPI_8PAD, 0x10, kFLEXSPI_Command_DUMMY_RWDS_DDR, kFLEXSPI_8PAD, 0x07),

[4 * HYPERRAM_CMD_LUT_SEQ_IDX_WRITEDATA + 2] = FLEXSPI_LUT_SEQ(

kFLEXSPI_Command_WRITE_DDR, kFLEXSPI_8PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0x00),

I am unsure how the operands are determined such as RADDR_DDR=0x18, CADDR_DDR=0x10 and WRITE_DDR=0x04. Also, as explained previously I am having some difficulty determining DUMMY_RWDS_DDR (the latency count as you say), based on the datasheet values.

I'd like to avoid a situation where I get a configuration that "just works", but then stops working when something in the system is changed (such as a different hyperram part) without me knowing how to modify the LUT and/or config. That's why I want to understand the LUT.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

I basic understand your demand, according to the Cypress HyperBus device, the Initial latency is 6, however, to consider the PCB length and routing, we need to increase the latency a bit.

Further, there's an Instruction execution on the SPI interface section in the RM to help you to understand.

Lastly, there's unnecessary to take a lot to get an optimal latency number, as compared with the prefetch and buffer feature, latency number only has a little effection to improve code execution.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------