- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Display on G133HAN01 LVDS using SN65dsi84 MIPI DSI LVDS bridge

Display on G133HAN01 LVDS using SN65dsi84 MIPI DSI LVDS bridge

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Display on G133HAN01 LVDS using SN65dsi84 MIPI DSI LVDS bridge

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using imx8m-ql custom board which has SN65DSI84 MIPI DSI LVDS bridge.

We are trying to bring up G133HAN01 LVDS panel display. We need to set the pixel clock between 134 MHZ to 145MHZ.

But the actual clock calculated is either 120Mhz (for pixelclock=134Mhz) or 150Mhz (for pixelclock=142Mhz). We tried hard coding the actual_clk value with LVDS pixelclock(134 Mhz to 145 Mhz), but there is no impact.

Also we tried to change Video PLL clock from 594 to 424. But it is not at all changing. See the below error log

[ 0.803268] dcss-core 32e00000.dcss: Configured video pll 2 with ref_clk 1 freq 594000000 (actual 594000000)

[ 0.883445] imx-drm display-subsystem: bound imx-dcss-crtc.0 (ops dcss_crtc_ops)

[ 0.940146] dcss-core 32e00000.dcss: pixel clock set to 150000000 Hz instead of 141000000 Hz, error is 9000000 Hz

How can we configure dcss to operate at 424 MHZ ? so that we will get pixel clock of 141 MHZ for our LVDS panel.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Antony,

I am very new to IMX processors, we are going to use imx8m. can you please tell the procedure, How to configure MIPI DSI to LVDS bridge with IMX8M board ?

Thanks and regards,

Srinu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

art

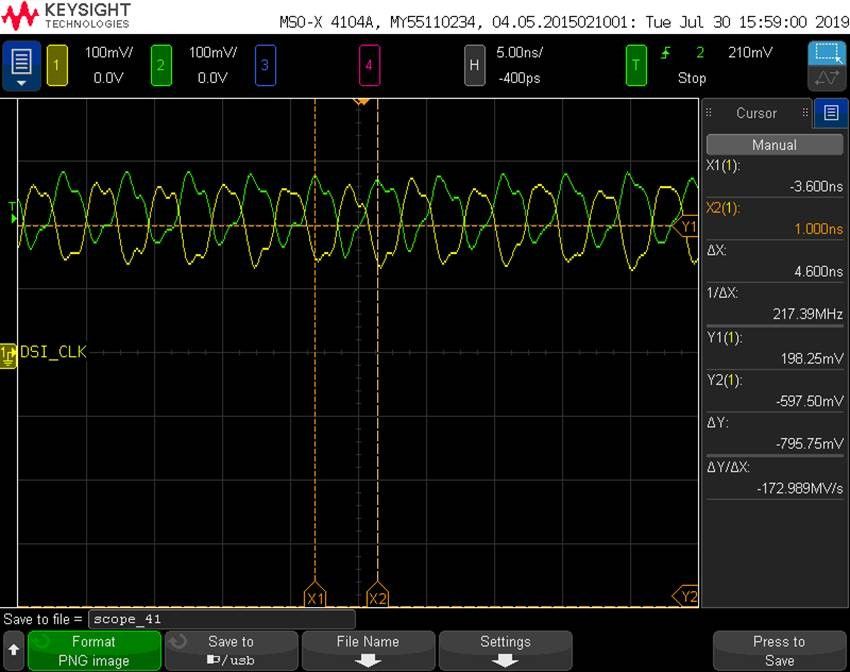

We have probed MIPI DSI signals coming out imx8m processor. From DSI tuner, suggested DSI clock is 222 MZH and DSI Ch A clock is 444 MHZ. CSR register 0x12 value is 0x58.

Below is our oscilloscope screenshot showing DSI clock as 218 MHZ. But we are expecting 444 MHZ.

DSI Clock frequency : 218MHz

DSI data activity

Please provide your feedback on DSI clock.

Why it is showing 218 MHZ instead of 444 MHZ?

Thanks,

Antony

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Antony,

From my current understanding, the MIPI DSI clock is double data rate. So 218MHz is about half of 444MHz. Using DDR, the same amount of data is sent using a clock with half the frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How do you configure the clock frequencies? Please specify the steps in details.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

We are using dcss as input source for LVDS display. Our custom board has MIPI DSI to LVDS bridge (SN65DSI84) to convert MIPI DSI signals to LVDS output signals.

We are configuring panel and DSI parameters using DSI tuner. Generated CSR values and using it in our custom driver.

Since our panel is a dual channel LVDS, we divided horizontal parameters by 2 and kept vertical parameters as it.

Similarly, for DSI input we multiplied horizontal parameters with 2 and kept vertical parameters as same. LVDS clock is divided by 2 (142000000/2).

Now the clock we are getting currently as below:

LVDS pixel clock = 71 MHZ

DSI clock = 426 MHZ

Please look into the generated CSR values.

char addresses[] = {

0x09, 0x0A, 0x0B, 0x0D, 0x10, 0x11, 0x12, 0x13,

0x18, 0x19, 0x1A, 0x1B, 0x20, 0x21, 0x22, 0x23,

0x24, 0x25, 0x26, 0x27, 0x28, 0x29, 0x2A, 0x2B,

0x2C, 0x2D, 0x2E, 0x2F, 0x30, 0x31, 0x32, 0x33,

0x34, 0x35, 0x36, 0x37, 0x38, 0x39, 0x3A, 0x3B,

0x3C, 0x3D, 0x3E, 0x0D

};

char values[] = {

0x00, 0x05, 0x28, 0x00, 0x26, 0x00, 0x55, 0x00,

0x6F, 0x00, 0x03, 0x00, 0x80, 0x07, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00, 0x21, 0x00, 0x00, 0x00,

0x15, 0x00, 0x00, 0x00, 0x0E, 0x00, 0x00, 0x00,

0x2C, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00, 0x01

};

Below is our configurations in .dts file:

DCSS configuration:

&dcss {

status = "okay";

disp-dev = "mipi_disp";

clocks = <&clk IMX8MQ_CLK_DISP_APB_ROOT>,

<&clk IMX8MQ_CLK_DISP_AXI_ROOT>,

<&clk IMX8MQ_CLK_DISP_RTRM_ROOT>,

<&clk IMX8MQ_CLK_DC_PIXEL>,

<&clk IMX8MQ_CLK_DUMMY>,

<&clk IMX8MQ_CLK_DISP_DTRC>;

clock-names = "apb", "axi", "rtrm", "pix_div", "pix_out", "dtrc";

assigned-clocks = <&clk IMX8MQ_CLK_DC_PIXEL>,

<&clk IMX8MQ_CLK_DISP_AXI>,

<&clk IMX8MQ_CLK_DISP_RTRM>;

assigned-clock-parents = <&clk IMX8MQ_VIDEO_PLL1_OUT>,

<&clk IMX8MQ_SYS1_PLL_800M>,

<&clk IMX8MQ_SYS1_PLL_800M>;

assigned-clock-rates = <594000000>,

<800000000>,

<400000000>;

dcss_disp0: port@0 {

reg = <0>;

dcss_disp0_mipi_dsi: mipi_dsi {

remote-endpoint = <&mipi_dsi_in>;

};

};

};

MIPI DSI and MIPI DSI bridge configuration:

&mipi_dsi {

status = "okay";

assigned-clocks = <&clk IMX8MQ_CLK_DSI_PHY_REF>,

<&clk IMX8MQ_CLK_DSI_CORE>,

<&clk IMX8MQ_VIDEO_PLL1_REF_SEL>,

<&clk IMX8MQ_VIDEO_PLL1>;

assigned-clock-parents = <&clk IMX8MQ_VIDEO_PLL1_OUT>,

<&clk IMX8MQ_SYS1_PLL_266M>,

<&clk IMX8MQ_CLK_25M>;

assigned-clock-rates = <24000000>,

<266000000>,

<0>,

<426000000>;

sync-pol = <1>;

pwr-delay = <10>;

port@1 {

mipi_dsi_in: endpoint {

remote-endpoint = <&dcss_disp0_mipi_dsi>;

};

};

};

&mipi_dsi_bridge {

status = "okay";

panel@0 {

reg = <0>;

status = "okay";

compatible = "auo,g133han01";

pinctrl-0 = <&pinctrl_panel>;

backlight = <&backlight>;

bridge-i2c-bus = <&i2c4>;

bridge-info = <4>;

bridge-gpios = <&gpio5 5 GPIO_ACTIVE_HIGH>;

enable-gpios = <&gpio1 0 GPIO_ACTIVE_HIGH>;

power-gpios = <&gpio5 3 GPIO_ACTIVE_HIGH>;

dsi-lanes = <4>;

panel-width-mm = <293>;

panel-height-mm = <165>;

port {

panel_in: endpoint {

remote-endpoint = <&mipi_dsi_bridge_out>;

};

};

};

port@1 {

mipi_dsi_bridge_out: endpoint {

remote-endpoint = <&panel_in>;

};

};

};

Still we are not display on LVDS (only backlight is working). We are getting a blank screen.

Anything we are missing here ?

Please provide your feedback.

Thanks,

Antony

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you correctly configured the SN65DSI84 bridge through its I2C control interface? Check with the oscilloscope the signal activity on both MIPI DSI and LVDS side of the bridge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

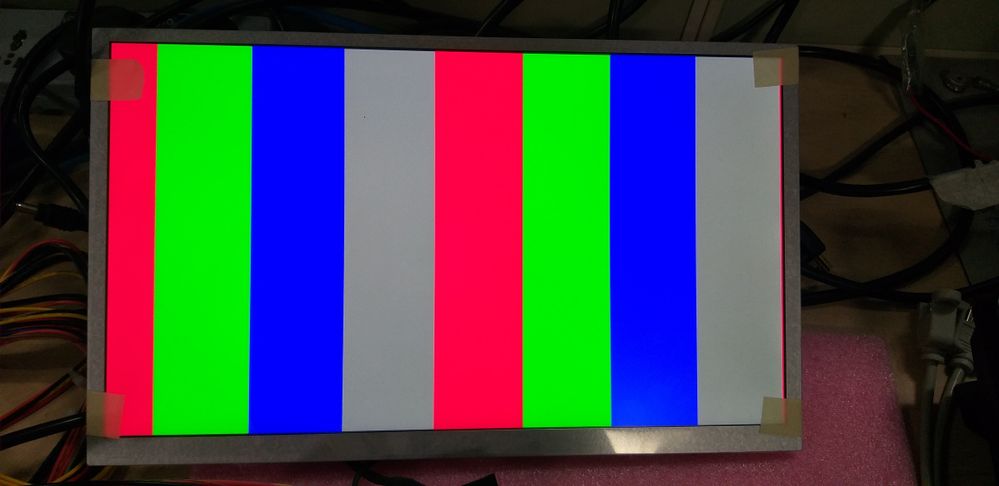

We have created test pattern in DSI tuner and we could able to display the test pattern successfully.

But when using actual DSI input, there is no display on LVDS.

We verified our initialization sequence of SN65DSI84 bridge and it looks like fine. Please find our initialization sequence below:

static int bridge_sn65dsi84_enable(struct panel_simple *p)

{

int i, err=0;

int chipid[] = {0x35, 0x38, 0x49, 0x53, 0x44, 0x20, 0x20, 0x20, 0x01};

char address, value;

if (p->bridge_gpio)

{

gpiod_set_value_cansleep(p->bridge_gpio, 0);

msleep(10);

gpiod_set_value_cansleep(p->bridge_gpio, 1);

msleep(10);

}

for (i = 0; i < sizeof(chipid) / sizeof(int); i++) {

address = (char)i;

err = sn65dsi84_i2c_read(p->bridge, &address, 1, &value, 1);

if (err < 0) {

printk("failed to read chip id\n");

return err;

}

if (value != chipid[i]) {

printk("chip id is not correct\n");

return err;

}

}

err = bridge_sn65dsi84_config(p);

if( err < 0)

return err;

msleep(50);

err = sn65dsi84_write_reg(p->bridge, 0x09, 0x01);

if (err < 0) {

printk("failed to write data to the chip\n");

return err;

}

msleep(50);

address = 0xe5;

err = sn65dsi84_i2c_read(p->bridge, &address, 1, &value, 1);

if (err < 0) {

printk("failed to read chip id\n");

return err;

}

msleep(500);

return 0;

}

Please advise if we are wrong.

What else we have to look to get the LVDS display ?

Please provide your feedback.

Thanks,

Antony

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have changed the clock for IMX8MQ_VIDEO_PLL1 from 599999999 to 424000000 in mipi_dsi node. Now we could able to set the pixel clock in LVDS clock range. Given 141000000 Hz as pixel clock and we got 141333333 Hz.

dcss-core 32e00000.dcss: pixel clock set to 141333333 Hz instead of 141000000 Hz, error is 333333 Hz

Even though the actual clock calculated is within the LVDS clock range, we did not get display.

Please share your inputs.