- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: About protection circuit for the USB VBUS/BP/BM signals to protect the latch-up in i.MX6DQ.

About protection circuit for the USB VBUS/BP/BM signals to protect the latch-up in i.MX6DQ.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir or Madam,

Hello.

My customer assume the case of connecting the USB OTG device with no input the power to i.MX6.

Until a power is supplied to MX6 from PMIC, is it necessary to design a protection circuit to the i.MX6DQ's USB VBUS/BP/BM signals, to protect the latch-up occurrence?

(BTW, the protection circuit isn't implemented on FSL's SABRE board)

Best Regards,

Keita

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

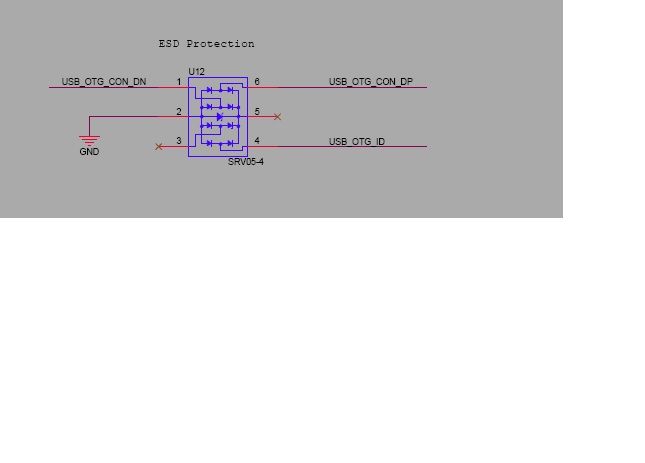

The USB OTG protection circuit is implemented on the i.MX6 SABRE SD board. Please refer to the schematic SPF-27392 Rev.C3, Sheet 11. These are the following protection components: U12, TVS1, Q512 to Q515 with surrounding circuits.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Artur, Yuri,

I am now confused. See 4.2.1 Power-Up Sequence note in i.MX 6Dual/6Quad Applications Processors for Industrial Products http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQIEC.pdf page 31:

USB_OTG_VBUS and USB_H1_VBUS are not part of the power supply sequence and can be powered at any time.

Note: Maybe, you were referring to Errata: ERR006281 USB: Incorrect DP/DN state when only VBUS is applied http://cache.freescale.com/files/32bit/doc/errata/IMX6DQCE.pdf but it says nothing about locking up or damaging the CPU ... it just may cause a problem if charger feature is used, which is logical.

From the datasheet note I understand, that VBUS can be connected anytime (even in case no other voltage is connected) and it will not affect booting process (e.g. locking up CPU) or damage CPU. Am I wrong or this is a mistake in datasheet?

Thank you very much for your confirmation.

- Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

"USB_OTG_VBUS and USB_H1_VBUS are not part of the power supply sequence

and can be powered at any time" - assuming VDD_VSNVS_IN is always (or, at least, first)

applied.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thank you for your reply.

I have an additional question.

Refer to schematic again.

I couldn't find the protection circuit for USB_OTG_DN / USB_OTG_DP.

If i.MX6 has no power, is it possible to input the power into i.MX6's D+/D-?

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, from the AI design :

USB_OTG_ID could cause backfeed through ESD Protection scheme, when

P3V3_DELAYED is not powered up. Therefore, pin 5 of the SRV05-4 is not

connected to a postive supply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

Sorry for my delay reply.

I have additional question.

My understanding is below.

When i.MX6 is not powered with connecting the PC and i.MX6 board, USB VBUS power = 0V protected by U12, TVS1, Q512, Q515 on i.MX6Q SABRE-AI.

But, I consider that "USB_OTG_DN" and "USB_OTG_DP" lines supplied the some voltage.

So, we worried about the latch-up by the voltage be applied from the USB differential-signal.

Is the protection circuit necessary for USB differential-signal line?

or

Are i.MX6's "USB_OTG_DN" and "USB_OTG_DP" pin state Hi-Z during power off?

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Note, in order to protect the i.MX6 processor, the USB 5V (VBUS) should not be applied to

the i.MX6 (VBUS pins), if VDD_VSNVS_IN is not powered on, because the LDO_USB internal

regulator requires VSNVS provided to work correctly.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The scheme, shown above is enough for USB D+ / D- signals protection.

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

Do you have any update?

Best Regards,

Keita