- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi,

I am using i.MX8M PLUS EVK.

I am investigating the default value of iomuxc register.

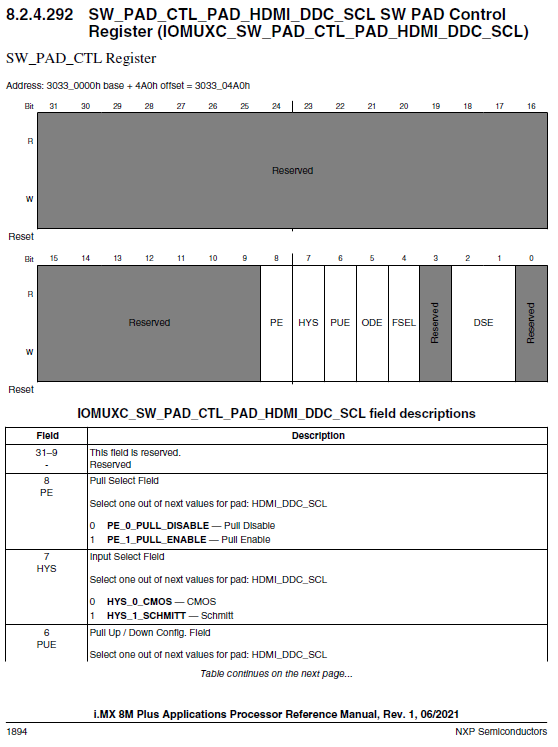

For example, The value of MX8MP_IOMUXC_HDMI_DDC_SCL is as follows.

root@imx8mpevk:~# cat /sys/kernel/debug/pinctrl/pinctrl-maps

...

device 30330000.pinctrl

state default

type CONFIGS_PIN (3)

controlling device 30330000.pinctrl

pin MX8MP_IOMUXC_HDMI_DDC_SCL

config 000001c3

On the other hand, the register definition in the [i.MX 8M Plus Applications Processor Reference Manual]

is as follows.

0x01c3 = 0001 1100 0011

It looks like the Reserved bit[0] is set to 1. What is the meaning of this?

Or, Is the register definition I'm referring to incorrect?

Thank you!

已解决! 转到解答。

@shinichiro_adac

Hello,

real configuration of the pin is as following:

root@imx8mpevk:/unit_tests# ./memtool -32 0x303304a0 1

E

Reading 0x1 count starting at address 0x303304A0

0x303304A0: 000001C2

The reserved bit is not used.

Regards,

Yuri.

> real configuration of the pin is as following:

Thank you for your reply.

I dumped all PAD/PINMUX registers in the same way.

By the way, the configuration of the pin is defined in DTS as follows.

https://source.codeaurora.org/external/imx/linux-imx.git

branch:lf-5.10.72-2.2.0

[arch/arm64/boot/dts/freescale/imx8mp-evk.dts]

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog>;pinctrl_hog: hoggrp {

fsl,pins = <

MX8MP_IOMUXC_HDMI_DDC_SCL__HDMIMIX_HDMI_SCL 0x400001c3

MX8MP_IOMUXC_HDMI_DDC_SDA__HDMIMIX_HDMI_SDA 0x400001c3

MX8MP_IOMUXC_HDMI_HPD__HDMIMIX_HDMI_HPD 0x40000019

MX8MP_IOMUXC_HDMI_CEC__HDMIMIX_HDMI_CEC 0x40000019

>;

};

1c3 = 0001 1100 0011

MX8MP_IOMUXC_HDMI_DDC_SCL__HDMIMIX_HDMI_SCL bit0 is set as 1.

Why is bit0 set in DTS?

If it is not set to the reserved bit, does it mean something else?

Thanks!

@shinichiro_adac

Hello,

real configuration of the pin is as following:

root@imx8mpevk:/unit_tests# ./memtool -32 0x303304a0 1

E

Reading 0x1 count starting at address 0x303304A0

0x303304A0: 000001C2

The reserved bit is not used.

Regards,

Yuri.