- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- AA104SH02-T1 display problem with imx257

AA104SH02-T1 display problem with imx257

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

AA104SH02-T1 display problem with imx257

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello :

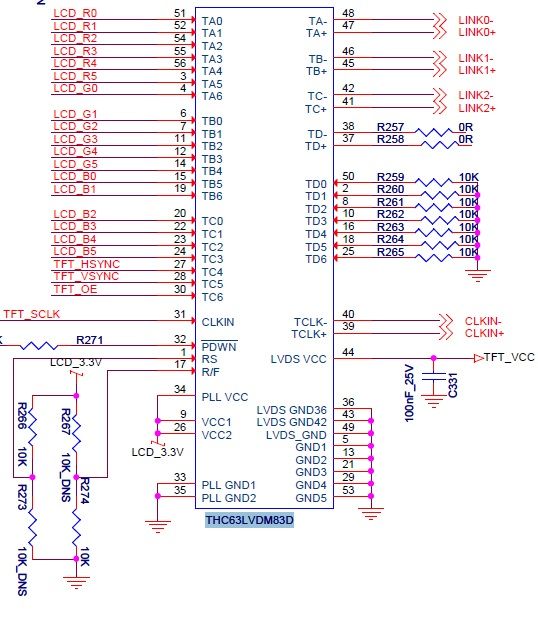

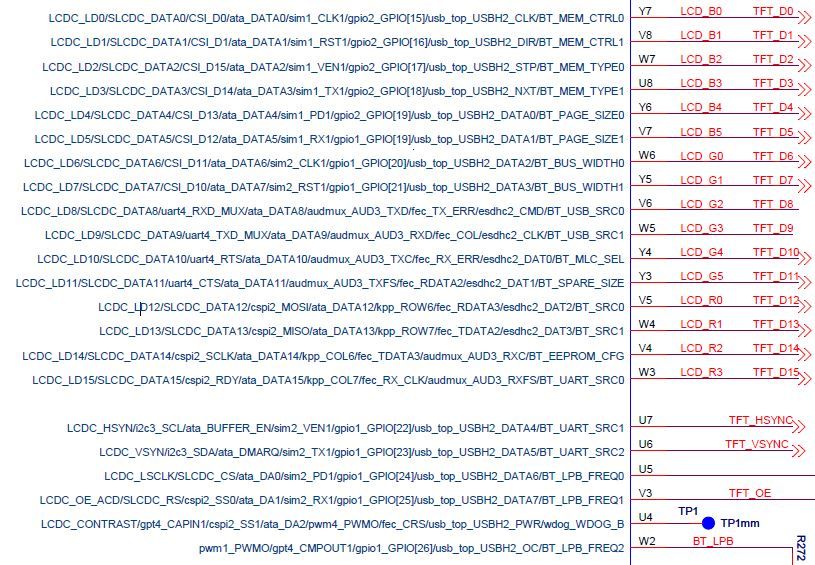

I am using the follow way connect to my lcd with lvds signal .I use th 16bpp mode ,

LCDC_LD0 which is R0 and LCDC_LD12 is B0. They should not active at all.

It is strange that the blue color is not working fine. I using qt to test it

When I set the RGB color to blue most in qt that is (0,0,255) ,it is B1 to B5 are all 1.

The screen looks like crash,nothing is display on the creen,but when I set blue to lower,

the value is below (0,0.180) then it behave normal.

However,the RED and green behave normal.

The AA104SH02 lcd only use the OE signal of the cpu.

It seems that the blue have influence to OE signal of LCD.

I have look the THC63LVDM83D manual ,it should match the requirment of the LCD.

I test it in uboot and linux ,it behave the same.

Can any one have some idea?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

another reason may be i.MX25 erratum "TLSbo95476 LCDC: LSCLK is missing",

that is:

LVDS requires a serialized stream where the RGB pixel data and LCD timing

are encapsulated. Using an external circuit which PLL base would be the PIXCLK,

the RGB data and timing could be serialized. This works for 12bpp and 16bpp but

unfortunately for 2bpp, 4bpp, 8bpp, 18bpp and 24bpp, LSCLK skips one cycle

every DE rising, every VSYNC rising and every VSYNC falling. These glitches do

not affect TFT panels because during this time all signals are ignored for the

TFT LCD panel but causes LVDS serialization to fail.

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor:

I am using 16bpp mode,so it should no influence.

And I have changed the PIXCLK to CLKO .But problem still exist.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi wang

reason may be SCLK jitter, as i.MX25 was not designed for lvds

converters usage. One can try to use appropriate clock from

CKO pin, using MCR register.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear igor:

I have try the CLKO as the clock in of the LVDS converter ,i measure the CLKO on the scope the frequency is 40MHz,

some time it is jump to 39.85MHz .

The result is same ,the color is wrong.

I am sure that the route of the board is correct. No signal connection wrong on PCB ,and no cable is wrong.

Best regards

wangl

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear igor:

The SCLK is LCDC_LSCLK of imx257 ,I measure on the scope it is 40MHz and it is stable.

I set the pcd to value 2,and set parent clk of lcdc_lsclk to upll which is 120MHz,so it is LCDC_LSCLK is 40MHz.