- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX处理器知识库

- :

- Porting LVDS LCD With Low Resolution to i.MX6

Porting LVDS LCD With Low Resolution to i.MX6

Porting LVDS LCD With Low Resolution to i.MX6

Porting LVDS LCD With Low Resolution to i.MX6

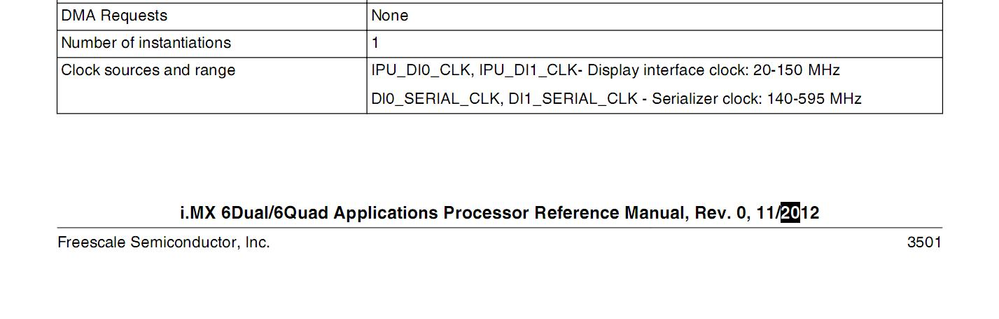

Some customers often use LVDS LCD with low resolution on i.MX6 platform, such as 320x240, but by defualt , linux bsp doesn't support low frequency pixel clock for LVDS module input.

Question:

When we port LVDS LCD with 320x240 resolution to android4.2.2, we found pixel clock is not correct, it always output 38.9MHz, it is no probem for big resolution , for example 1024x768, but the clock we need for 320x240 LCD is 6.4MHz.

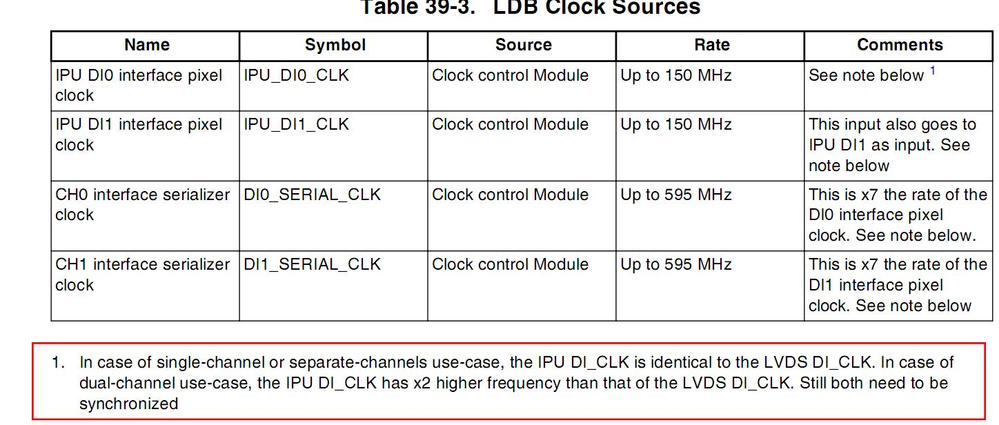

According to the quesiton, Let us check IPU & LDB clock in i.MX6 datasheet at first :

From above table, if ldb clock is from IPU, we will not get 6.4MHz pixel clock, so we will have to adjust its source clock:

The following steps are procedure that ports LVDS LCD with 320x240 resolution to i.MX6Q.

1. Adding LVDS LCD timing structure to ldb.c

static struct fb_videomode ldb_modedb[] = {

{

"LDB-XGA", 60, 320, 240, 155914,

38, 20,

15, 4,

30, 3,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,

},

| { |

"LDB-1080P60", 60, 1920, 1080, 7692,

100, 40,

30, 3,

10, 2,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

| }; |

2.Modifying clock source of ldb module

Checking /arch/arm/mach-mx6/clock.c, we can find there are 3 ldb's clock source : &pll5_video_main_clk, &pll2_pfd_352M, &pll2_pfd_400M,

static int _clk_ldb_di1_set_parent(struct clk *clk, struct clk *parent)

{

u32 reg, mux;

int rev = mx6q_revision();

reg = __raw_readl(MXC_CCM_CS2CDR)

& ~MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_MASK;

mux = _get_mux6(parent, &pll5_video_main_clk,

&pll2_pfd_352M, &pll2_pfd_400M,

(rev == IMX_CHIP_REVISION_1_0) ?

&pll3_pfd_540M : /* MX6Q TO1.0 */

&mmdc_ch1_axi_clk[0], /* MX6Q TO1.1 and MX6DL */

&pll3_usb_otg_main_clk, NULL);

reg |= (mux << MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_OFFSET);

__raw_writel(reg, MXC_CCM_CS2CDR);

return 0;

}

By default, pll2_pfd_352M is configured as the clock source of ldb:

clk_set_parent(&ldb_di0_clk, &pll2_pfd_352M);

clk_set_parent(&ldb_di1_clk, &pll2_pfd_352M);

We should change the clock source to be pll5_video_main_clk

clk_set_parent(&ldb_di0_clk, &pll5_video_main_clk,);

clk_set_parent(&ldb_di1_clk, &pll5_video_main_clk,);

3. Configuring initial clock in board-mx6q_sabresd.c

static struct ipuv3_fb_platform_data sabresd_fb_data[] = {

{ /*fb0*/

.disp_dev = "ldb",

.interface_pix_fmt = IPU_PIX_FMT_RGB666,

.mode_str = "LDB-XGA",

.default_bpp = 16,

.int_clk = false,

.late_init = false,

}

int_clk=false means LDB clock is from PLL2_PFD_352 or pll5_video_main_clk; int_clk=true mean LDB clock if from IPU.

OK, after doing above steps, LVDS LCD with low resolution should normally work.

Freescale TICS team

Weidong.sun

2015-08-18

Hello Weidong,

We use i.MX6 quad platform and our kernel verison is 3.10.53.

We can use lvds lcd with 1024x768/65M on i.MX6 quad platform successfully, but we get problem when we change the resolution of lvds lcd to 640x240/13M.

So, we follow your steps above and try to see whether we can get 6.4M pixel clock. The test fails.

The below is lvds setting we use:

1. Adding lvds lcd timing structure on arch\arm\boot\dts\lec-imx6.dtsi

lvds-channel@0 {

fsl,data-mapping = "spwg"; /* spwg or jeida */

fsl,data-width = <24>;

primary;

status = "okay";

display-timings {

native-mode = <&timing0>;

timing0: hsd100pxn1 {

clock-frequency = <6400000>;

hactive = <320>;

vactive = <240>;

hback-porch = <38>;

hfront-porch = <20>;

vback-porch = <15>;

vfront-porch = <4>;

hsync-len = <30>;

vsync-len = <3>;

};

};

};

2. Modifying clock source of ldb module on arch\arm\mach-imx\clk-imx6q.c

/*

* Kernel parameter 'ldb_di_clk_sel' is used to select parent of ldb_di_clk,

* among the following clocks.

* 'pll5_video_div'

* 'pll2_pfd0_352m'

* 'pll2_pfd2_396m'

* 'mmdc_ch1_axi'

* 'pll3_usb_otg'

* Example format: ldb_di_clk_sel=pll5_video_div

* If the kernel parameter is absent or invalid, pll2_pfd0_352m will be

* selected by default.

*/

// modified by johnson here

static int ldb_di_sel = 0;

3. Configuring initial clock on arch\arm\boot\dts\lec-imx6.dtsi

mxcfb3: fb@2 { /* IPU2 DI0: /dev/fb3=LVDS, fb4=IPU2's overlay

* Solo/DL: IPU1, fb2 shared with par. RGB, no overlay */

compatible = "fsl,mxc_sdc_fb";

disp_dev = "ldb";

interface_pix_fmt = "RGB666";

default_bpp = <16>;

int_clk = <0>;

late_init = <0>;

status = "okay";

};

Do you have any suggestion about this problem???

Hi,

I have a LCD display with same resolution 240*320 . The kernel is 3.10.53 for Lollipop. So I am using dtsi files. We are expecting 5.6 or 7 MHZ but always getting 24 Mhz when PLL5 clock is used instead of PLL2 . Did you able to set 6.4M pixel clock for your board?.. Other than the changes documented by Wigros Sun , any other additional changes required for Low resolution LCD to work on I.MX6 with kernel version 3.10.53?

Thanks & Regards,

Anjali