- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Re: QSPI I/03 Diven Low during all Single bit accesses

QSPI I/03 Diven Low during all Single bit accesses

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

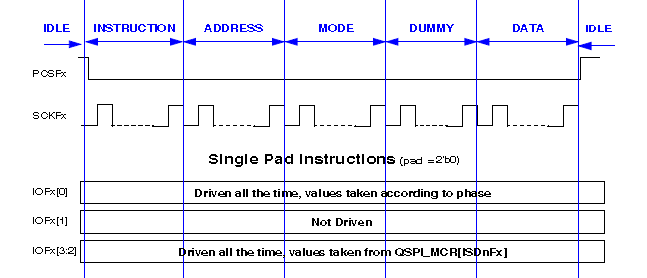

I the QSPI flash device we are using has a hold feature on I/O pin 3 during all single PAD accesses this pin is being driven low, placing the QSPI device into hold. The reference manual says these pins are always driven during single pad instructions. and the value driven is taken from QSPI_MCR[ISDnFx] in figure 30-2. The QSPI-MCR has no definition for these bits. Another not is for bootmode using QSPI do you drive the IO_3 bit high or low? Below is the captured image from the reference manual.

Regards,

Jon Partee

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Edward,

You are apparently correct, and the Figure 30-2 is to be corrected accordingly, too.

Sincerely, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jon,

I am having difficulties understanding your request.

May you, please, reformulate it, using punctuation and quotes (") for the signal and pin names, and referring to relevant sections of the Reference Manual counting a few thousand pages?

BTW, before we proceed further, have you reviewed our software published on the Web, specifically the piece responsible for QSPI control, to see how Vybrid does it?

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Naoum, it was quite clear:

1) RM Rev. 5, p. 1192, p.1193 mention QSPI_MCR register bits named ISD3FA, ISD2FA, ISD3FB, ISD2FB. Also the same bits are named as ISDnFx. But on p.1207, where QuadSPIx_MCR register is explained, there's no mention for ISDnFx bits! It is not clear for example which bit in QSPI_MCR is ISD3FA.

BTW why in one place module is called QSPI, in another place QuadSPI? Yes, we know that it is the same thing, but different names make it hard to search in those few thousand pages.

2) Purpose of ISDnFx bits would be quite clear if these would be documented properly. Since QSPI memory chips can work as single pin SPI devices, ISDnFx bits could define WP\DATA2 and HOLD\DATA3 pins state in single (and 2x?) pin mode. The question is how these pins are driven at boot time, when boot device is QSPI. Where should one set up ISDnFx bits for boot.

I wonder which "software published on the Web" do you refer? URL please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Edward and Jon,

Are you asking about the data width and how to configure it? -Please, take a look at the https://community.freescale.com/message/346778#346778 thread.

Sincerely, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Concern is not about data width, but about pins corresponding to data bits 2 and 3 when QSPI is configured for 1 bit mode. According to RM Rev. 5 pages 1192-1193 these pins are always driven by Vybrid, and pin levels are set up using ISDnFx bits in QaudSPIx_MCR register. But RM doesn't tell which bits in QaudSPIx_MCR are actually ISDnFx bits. I have MQX installed on my PC and found and see there MVF50GS10MK50.h file. Unfortunately it also doesn't list any ISDnFx bits. Only following MCR bits are defined.

#define QuadSPI_MCR_SWRSTSD_MASK 0x1u

#define QuadSPI_MCR_SWRSTSD_SHIFT 0

#define QuadSPI_MCR_SWRSTHD_MASK 0x2u

#define QuadSPI_MCR_SWRSTHD_SHIFT 1

#define QuadSPI_MCR_DQS_EN_MASK 0x40u

#define QuadSPI_MCR_DQS_EN_SHIFT 6

#define QuadSPI_MCR_DDR_EN_MASK 0x80u

#define QuadSPI_MCR_DDR_EN_SHIFT 7

#define QuadSPI_MCR_CLR_RXF_MASK 0x400u

#define QuadSPI_MCR_CLR_RXF_SHIFT 10

#define QuadSPI_MCR_CLR_TXF_MASK 0x800u

#define QuadSPI_MCR_CLR_TXF_SHIFT 11

#define QuadSPI_MCR_MDIS_MASK 0x4000u

#define QuadSPI_MCR_MDIS_SHIFT 14

#define QuadSPI_MCR_DOZE_MASK 0x8000u

#define QuadSPI_MCR_DOZE_SHIFT 15

I guess that perphaps Vybrid doesn't drive QSPI bits 2 and 3 in single bit mode. Unfortunately I don't have working Vybrid board at hand, I'd like to check if these pins are driven in single bit mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Gentlemen,

I will try to clarify this issue.

Regarding the naming convention and deviations from it - we are all humans, especially while writing a document several thousand pages long :smileyhappy:; nonetheless, I will report these deviations to our Technical Writing team.

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Naoum,

As you noted, the inconsistent naming conventions are the secondary issue.

The initial unanwered question from Jon Partee (and clarified by Edward) remains...

"The QSPI flash device we are using has a hold feature on I/O pin 3 during all single PAD accesses this pin is being driven low, placing the QSPI device into hold. The reference manual says these pins are always driven during single pad instructions. and the value driven is taken from QSPI_MCR[ISDnFx] in figure 30-2. The QSPI-MCR has no definition for these bits."

Any clarification on these bits is greatly appreciated.

Many thanks for your efforts,

Gordy Carlson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Gentlemen,

It appears that the bits mentioned but not described are no longer to be touched by a user - their default values are to be kept, so their names are to be removed from the Reference Manual.

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Naoum, thank you for this information.

Does it also mean that IOF[3:2] pads are not driven in 1- and 2-bit modes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Edward,

You are apparently correct, and the Figure 30-2 is to be corrected accordingly, too.

Sincerely, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

naoumgitnik can you continue with the follow up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Edward,

- Thanks for your clarification.

- Please, take a look at VF6xx Product Summary Page, specifically the Run-time Software.

- Regarding using both full (QuadSPI) and shorter (QSPI) names: according to our convention, the former is used for the block itself, and the latter for its signals, registers, etc.

- Sincerely, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naoum

Thanks for your reply and URL. I asked, because you have adviced few times to look for your sample code when documentation is not clear. Well, Run-time Software in summary page points to dozen of third party softwares, which may take half of my life finding required license info, pricing and finaly small piece of information I'm looking for. I had hope to get your advice which of these is really easy to look at and find information that is missing in current Rev. 5 RM and latest datasheet.

- Regarding using both full (QuadSPI) and shorter (QSPI) names: according to our convention, the former is used for the block itself, and the latter for its signals, registers, etc.

So is it correct that on page 1192 I see QSPI_MCR[ISD3FA] "standard" for referencing QSPI MCR register and its bit, and on page 1207 I see the same register called QuadSPIx_MCR? In both cases it the same thing, MCR register of QSPI (or QuadSPI) module.

Best Regards

Edward