- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- Vybrid プロセッサ

- :

- MQX Interrupt Shared Peripheral Routing

MQX Interrupt Shared Peripheral Routing

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MQX Interrupt Shared Peripheral Routing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

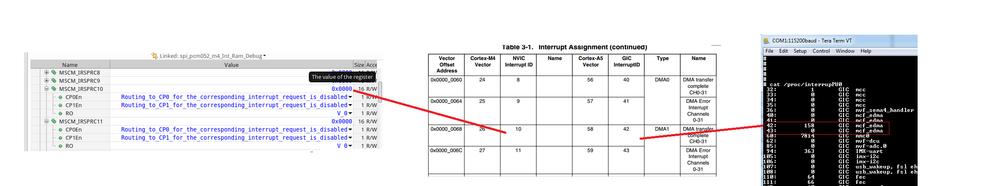

Reading the Vybrid AN4947.pdf, and in 4.2 Dual-core communication and synchronization options,

• Interrupts. Routing options for both cores — none, one, or both cores can be notified for the event.

I wanted for M4 MQX NVIC Interrupt 10 and 11 not to be shared on the A5 Linux.

I use this code to configure the routing.

/* Disable shared interrupt to A5 Core */

_irouter_routing(26,0,0);

_irouter_routing(27,0,0);

However it is not working. A5 Linux could still received and processed the interrupts.

Any ideas what I missed?

I'm using MQX Version 4.1.1

Thanks,

Carlo Val

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

alejandrolozano are you able to help here?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'd like to reproduce the behavior first. Carlo, which Linux BSP are you using?

Best Regards,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm using Linux version 3.0.15-ts-armv7l .

I saw yesterday in a file init_gic.c routing all interrupts to Core 1.

Ill try it today and see if it will work

Here is my update would be:

volatile uint16_t *ptr26;

volatile uint16_t *ptr27;

ptr26 = &MSCM_IRSPRC26;

*ptr26 = MSCM_IRSPRC_CP1En_MASK; /* route interrupts to core 1*/

ptr27 = &MSCM_IRSPRC27;

*ptr27 = MSCM_IRSPRC_CP1En_MASK; /* route interrupts to core 1*/

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlo,

Did you modification work?

Regards,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello alejandrolozano,

No it didn't work :-(

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

On Linux side you could try to disable the interrupt routed to the A5 corresponding to the DMA.

void mvf_init_irq(void)

{

unsigned int i;

void __iomem *int_router_base =

MVF_IO_ADDRESS(MVF_MSCM_INT_ROUTER_BASE);

struct irq_desc *desc;

unsigned short route;

/* start offset if private timer irq id, which is 29.

* ID table:

* Global timer, PPI -> ID27

* A legacy nFIQ, PPI -> ID28

* Private timer, PPI -> ID29

* Watchdog timers, PPI -> ID30

* A legacy nIRQ, PPI -> ID31

*/

gic_init(0, 27, MVF_IO_ADDRESS(MVF_INTD_BASE_ADDR),

MVF_IO_ADDRESS(MVF_SCUGIC_BASE_ADDR + 0x100));

for (i = MXC_INT_START; i <= MXC_INT_END; i++) {

desc = irq_to_desc(i);

desc->irq_data.chip->irq_set_wake = mvf_gic_irq_set_wake;

}

mvf_register_gpios();

int_router_base += 0x80;

for (i = 0; i < 112; i++) {

route = 1 | __raw_readw(int_router_base);

__raw_writew(route, int_router_base);

int_router_base += 2;

}

}

This function is found at vim arch/arm/mach-mvf/irq.c

Let me debug the M4 (MQX side) to verify the possible problem.

Best Regards,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlo,

Did you try the previous suggestion?

Best Regards,

Alejandro