- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- Vybrid プロセッサ

- :

- DDRMC_PHY02 Register Reserved Bits?

DDRMC_PHY02 Register Reserved Bits?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

DDRMC_PHY02 Register Reserved Bits?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

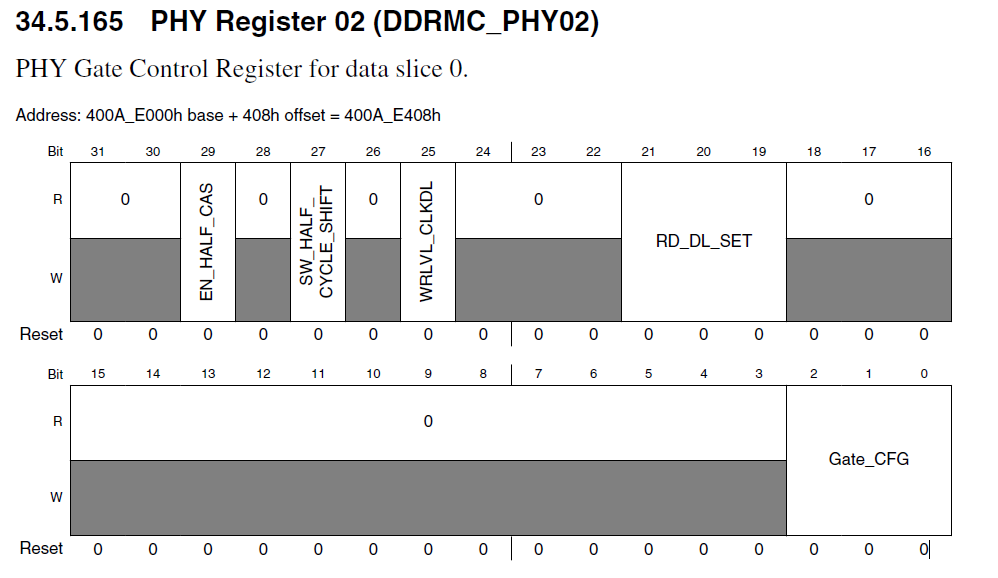

The file ddr.c included with the Freescale tower example source code sets 0x01210080 in the PHY02,18,&34 registers. When looking at the Vybrid reference manual (Rev 5, 07/2013) bits 7, 16 and 24 are set within the Reserved areas of the PHY Register 2 is set. When I write 0xFFFFFFFF to that register I'm able to read back 0xFFFFFFFF which doesn't agree with the reference manual documentation.

What are the reserved register bits that are set within the PHY02 register? Is the reference manual documentation correct?

ddr.c - source code

// phy_gate_lpbk_ctrl_reg freq set 0 |

reg32_write(DDR_PHY002, PHY_CTRL); // read delay bit21:19

reg32_write(DDR_PHY018, PHY_CTRL); // phase_detect_sel bit18:16

reg32_write(DDR_PHY034, PHY_CTRL); // bit lpbk_ctrl bit12

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear rmcginnis,

- Bits like the ones mentioned, i.e. those whose values are changed by our code but described as "Reserved" in the documentation, are "For Internal Use Only". In this case, customers are supposed to use our values, the bits' functions being considered confidential.

- Another type of bits, whose values are "Don't Care", are simply not used; it usually happens when a block is designed for more than one chip, and in the specific chip the specific bit's function is not used. (Example - a register (designed for the entire controller family) controls parameters for 2 USB channels, but the specific family member with a smaller-size package only has one USB channel bonded out.)

Regards, Naoum Gitnik.