- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

hello?

I'm using S32k144. To apply SCST, I purchased and applied SCST_M4_S32K144_RTM_1.0.10 version.

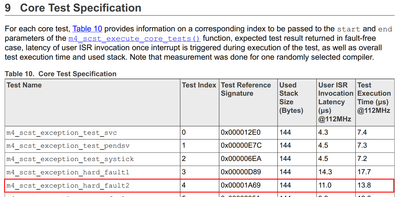

When performing a core test, an error occurs in item 4 as shown below.

It doesn't work anymore.

The development environment is using IAR 9.20.3 plug-in to s32ds arm 2.2.

What should I do?

已解决! 转到解答。

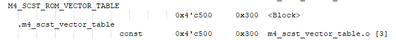

Size of the m4_scst_vector_table section should be 768 bytes (please see User Manual, Table 8. SCST Library Custom Section Size), so its ok.

Aligning a section to 128 bytes means that the starting address of that section should be divisible by 128 with no remainder. That is also ok on your side, because your starting address meets this requirement.

For more details about the reason for alignment, please see ARM®v7-M Architecture Reference Manual, chapter Vector Table Offset Register.

Hello,

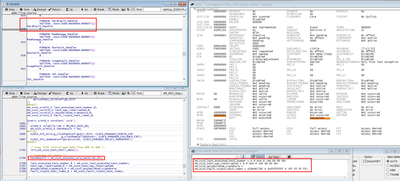

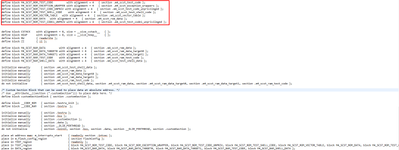

Could you please send us a screenshot of the values of core registers and also data, which are stored on stack, when stopped at m4_scst_exception_test_hard_fault2, row269? (Please see attachment, similar values shall be stored also in your registers)

Is MPU enabled? If Yes, could you please send us its configuration?

Could you please send us map file containing SCST related sections, to know about its address allocation?

Thanks for your reply.

I have attached a screen shot containing your requested information.

Also, please refer to the map file section related to scst below.

(Please understand that we are only delivering map files limited by company regulations.)

Is there anything else I can tell you?

m4_scst_ISR_address 0x2000'1c84 Data Gb m4_scst_exception_wrappers.o [3]

m4_scst_ISR_dispatcher 0x4'c9d5 Code Gb m4_scst_exception_wrappers.o [3]

m4_scst_VTABLE 0x4'9480 Data Gb m4_scst_vector_table.o [3]

m4_scst_accumulated_signature

0x1fff'8e7c Data Gb m4_scst_lib.o [3]

m4_scst_alu_test1 0x4'9c95 Code Gb m4_scst_alu_test1.o [4]

m4_scst_alu_test2 0x3'c279 Code Gb m4_scst_alu_test2.o [4]

m4_scst_alu_test3 0x4'71d5 Code Gb m4_scst_alu_test3.o [4]

m4_scst_alu_test4 0x3'8855 Code Gb m4_scst_alu_test4.o [4]

m4_scst_alu_test5 0x4'a145 Code Gb m4_scst_alu_test5.o [4]

m4_scst_alu_test6 0x4'85c9 Code Gb m4_scst_alu_test6.o [4]

m4_scst_alu_test7 0x4'c151 Code Gb m4_scst_alu_test7.o [4]

m4_scst_atomic_test_desc

0x4'b728 0x160 Data Gb m4_scst_data.o [5]

m4_scst_branch_test1 0x4'634b Code Gb m4_scst_branch_test1.o [4]

m4_scst_branch_test2 0x4'8927 Code Gb m4_scst_branch_test2.o [4]

m4_scst_branch_test3 0x4'9a2d Code Gb m4_scst_branch_test3.o [4]

m4_scst_check_flags_cleared

0x3'b141 Code Gb m4_scst_lib.o [3]

m4_scst_check_q_flag 0x3'b14f Code Gb m4_scst_lib.o [3]

m4_scst_clear_flags 0x3'b135 Code Gb m4_scst_lib.o [3]

m4_scst_exception_bus_fault

0x4'b889 Code Gb m4_scst_exception_test_bus_fault.o [4]

m4_scst_exception_hard_fault1

0x4'8f31 Code Gb m4_scst_exception_test_hard_fault1.o [4]

m4_scst_exception_hard_fault2

0x4'9efd Code Gb m4_scst_exception_test_hard_fault2.o [4]

m4_scst_exception_mem_fault

0x4'c90d Code Gb m4_scst_exception_test_mem_fault.o [4]

m4_scst_exception_test_handler_thread

0x4'9781 Code Gb m4_scst_exception_test_handler_thread.o [4]

m4_scst_exception_test_masking

0x4'b011 Code Gb m4_scst_exception_test_masking.o [4]

m4_scst_exception_test_nmihf

0x4'a5c5 Code Gb m4_scst_exception_test_nmihf.o [4]

m4_scst_exception_test_pendsv

0x4'cbf1 Code Gb m4_scst_exception_test_pendsv.o [4]

m4_scst_exception_test_svc

0x4'ca99 Code Gb m4_scst_exception_test_svc.o [4]

m4_scst_exception_test_systick

0x4'cc85 Code Gb m4_scst_exception_test_systick.o [4]

m4_scst_exception_test_tail

0x4'9389 Code Gb m4_scst_exception_lib.o [3]

m4_scst_exception_test_tail_chain

0x4'c751 Code Gb m4_scst_exception_test_tail_chain.o [4]

m4_scst_exception_test_tail_end

0x4'93d1 Code Gb m4_scst_exception_lib.o [3]

m4_scst_exception_test_tail_end_systick

0x4'93e9 Code Gb m4_scst_exception_lib.o [3]

m4_scst_exception_usage_fault

0x4'b201 Code Gb m4_scst_exception_test_usage_fault.o [4]

m4_scst_execute_core_tests

0x3'3c91 0xe4 Code Gb m4_scst_test_shell.o [5]

m4_scst_fault_inject_test_index

0x1fff'8e78 0x4 Data Gb m4_scst_test_shell.o [5]

m4_scst_fault_inject_value

0x1fff'8e70 0x4 Data Gb m4_scst_test_shell.o [5]

m4_scst_fetch_test 0x4'ce2d Code Gb m4_scst_fetch_test.o [4]

m4_scst_isr_return_address

0x2000'1c7c Data Gb m4_scst_lib.o [3]

m4_scst_last_executed_test_number

0x1fff'8e6c 0x4 Data Gb m4_scst_test_shell.o [5]

m4_scst_link_register_dump

0x2000'1c78 Data Gb m4_scst_lib.o [3]

m4_scst_loadstore_test1

0x4'685d Code Gb m4_scst_loadstore_test1.o [4]

m4_scst_loadstore_test2

0x4'531d Code Gb m4_scst_loadstore_test2.o [4]

m4_scst_loadstore_test3

0x4'8239 Code Gb m4_scst_loadstore_test3.o [4]

m4_scst_loadstore_test4

0x4'7a69 Code Gb m4_scst_loadstore_test4.o [4]

m4_scst_loadstore_test5

0x4'1f5d Code Gb m4_scst_loadstore_test5.o [4]

m4_scst_loadstore_test6

0x4'4d65 Code Gb m4_scst_loadstore_test6.o [4]

m4_scst_mac_test1 0x4'5891 Code Gb m4_scst_mac_test1.o [4]

m4_scst_mac_test2 0x4'413d Code Gb m4_scst_mac_test2.o [4]

m4_scst_nvic_registers_dump

0x2000'1c60 Data Gb m4_scst_lib.o [3]

m4_scst_pass_control_to_user_interrupt

0x4'ca6f Code Gb m4_scst_exception_wrappers.o [3]

m4_scst_regbank_test1 0x3'df21 Code Gb m4_scst_regbank_test1.o [4]

m4_scst_regbank_test2 0x3'eb35 Code Gb m4_scst_regbank_test2.o [4]

m4_scst_regbank_test3 0x3'f741 Code Gb m4_scst_regbank_test3.o [4]

m4_scst_regbank_test4 0x4'b3e9 Code Gb m4_scst_regbank_test4.o [4]

m4_scst_regbank_test5 0x4'cda9 Code Gb m4_scst_regbank_test5.o [4]

m4_scst_regbank_test6 0x4'3951 Code Gb m4_scst_regbank_test6.o [4]

m4_scst_restore_dedicated_registers_content

0x4'92d5 Code Gb m4_scst_exception_lib.o [3]

m4_scst_restore_registers_content

0x4'9313 Code Gb m4_scst_exception_lib.o [3]

m4_scst_scb_registers_dump

0x2000'1c48 Data Gb m4_scst_lib.o [3]

m4_scst_set_flag_test_was_interrupted

0x4'ca4f Code Gb m4_scst_exception_wrappers.o [3]

m4_scst_set_scst_interrupt_vector_table

0x4'9279 Code Gb m4_scst_exception_lib.o [3]

m4_scst_simdsat_test1 0x4'3105 Code Gb m4_scst_simdsat_test1.o [4]

m4_scst_simdsat_test2 0x4'4751 Code Gb m4_scst_simdsat_test2.o [4]

m4_scst_simdsat_test3 0x4'5df1 Code Gb m4_scst_simdsat_test3.o [4]

m4_scst_simdsat_test4 0x4'034d Code Gb m4_scst_simdsat_test4.o [4]

m4_scst_special_condition_flag

0x2000'1c74 Data Gb m4_scst_lib.o [3]

m4_scst_spr_registers_dump

0x2000'1c2c Data Gb m4_scst_lib.o [3]

m4_scst_status_test1 0x4'7e71 Code Gb m4_scst_status_test1.o [4]

m4_scst_status_test2 0x4'aa09 Code Gb m4_scst_status_test2.o [4]

m4_scst_status_test3 0x4'b9e9 Code Gb m4_scst_status_test3.o [4]

m4_scst_store_registers_content

0x4'924d Code Gb m4_scst_exception_lib.o [3]

m4_scst_test_tail_end 0x3'b159 Code Gb m4_scst_lib.o [3]

m4_scst_test_was_interrupted

0x1fff'8e74 0x4 Data Gb m4_scst_test_shell.o [5]

m4_scst_user_VTOR 0x2000'1c80 Data Gb m4_scst_exception_wrappers.o [3]

Thank you for the additional information.

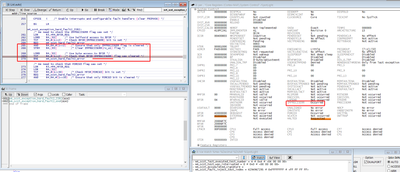

Could you please send us the screenshot from Trace32 with execution stopped in m4_scst_exception_hard_fault2, line 383? (Please see attachment)

If line 383 is not reachable, please check line 371.

Additionally, what value does your M4_DEVICE_RESERVED_ADDR have?

Also please, what 32-bit data is stored at address 0x4A124?

Hi. martinkaspar-r3

thank you for reply.

The current issue has been resolved.

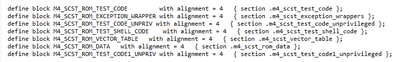

It seems to have occurred because the Rom section related to scst was not specified in my .icf file.

After adding the ROM section, it works without any issues.

As I mentioned before, when I added a global variable or text code, scst failed, and the number of tests that failed was random.

Looking at this, it was predicted to be influenced by alignment.

Is the way I solved it correct?

Or is there a better solution?

If there are any additional mistakes I made, please let me know.

Hi. thank you for your reply.

in SCST manual, i can't fine information that m4_scst_vector_table must be aligned to 128 bytes.

Can you find page and how to change my section.

Thank you every time.

Sorry for a confusion. Data, which is stored in section m4_scst_vector_table is being aligned to 128 bytes implicitly by SCST code and no user action is needed, therefore it is not mentioned in SCST UM. If section is not aligned to 128 bytes, it would still work, but size of the section would be increased due to the alignment.

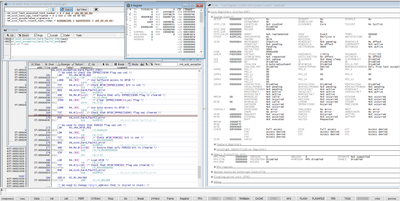

My current code size is 768 bytes.

How do I reduce it to 128 bytes?

Can I delete alignment = 4 in the define lists in the photo attached below?

Please guide me on how to do this.

Thank you for always explaining in detail.

Size of the m4_scst_vector_table section should be 768 bytes (please see User Manual, Table 8. SCST Library Custom Section Size), so its ok.

Aligning a section to 128 bytes means that the starting address of that section should be divisible by 128 with no remainder. That is also ok on your side, because your starting address meets this requirement.

For more details about the reason for alignment, please see ARM®v7-M Architecture Reference Manual, chapter Vector Table Offset Register.