- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: Unhandled Exception in Eth_43_GMAC_Init

Unhandled Exception in Eth_43_GMAC_Init

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Unhandled Exception in Eth_43_GMAC_Init

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I set up a binary for S32K358 with the Eth_43_GMAC_TS_T40D34M30I0R0 Driver and get an unhandled exception durring Start-Up in the Init of the driver .

The exception appears at the beginning of the DMA Initializing (See chapter 75.16.1 of S32K3xx Reference Manual, Rev. 5, 09/2022) in Gmac_Ip_InitDMA() after the software reset is provided. The highlevel-code looks like this:

Base = Gmac_apxBases[Instance];

/* Provide a software reset. */

Base->DMA_MODE |= GMAC_DMA_MODE_SWR_MASK;

In lowlevel this instructions are swapped. I think this happens due to compiler optimizations of the GreenHills-Compiler. But I am not realy sure if this is the problem here.

Now the question is, why this is happening? Do I need to configure the DMA at another point (for example in the Mcu module?). Or does the problem lie elsewhere?

Please help me at this point.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

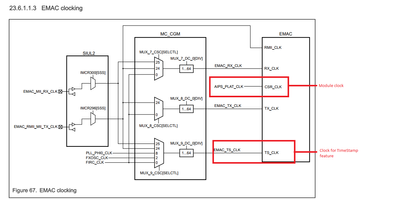

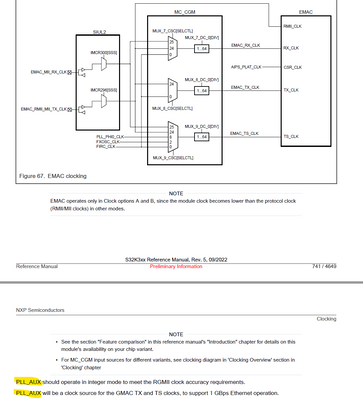

You need to ensure provide clock for CSR_CLK to ETH module can operate.

Best regards,

Nhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Nhi_Nguyen,

thank you for your hint. I reconfigured my environment, so the AIPS_CLK is used here as module clock. The exception still appears.

BR,

Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi BenjaminKubitsc

Can you please capture value of registers in GMAC before you run the command that write to DMA register? I still think that your issue come from GMAC's clock wasn't provided.

Best regards,

Nhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Nhi_Nguyen,

the GMAC_0 Peripherial Clock is enabled.

Unfortunately I don't have permission to attach images here, I can't capture the GMAC register range starting at 0x40484000 with the debugger, this is where the error is displayed: "Can not access target memory"

BR,

Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @BenjaminKubitschek ,

Can you please send me MCU configuration file that you're using?

Best regards,

Nhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Nhi_Nguyen,

sry for the late reply. Here is my config export of eth and mcu

Is there a way to organize a debug session? Please let me know about this.

Thank you.

BR, Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

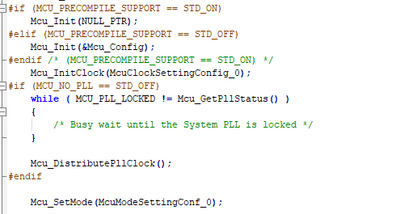

Hi @BenjaminKubitschek ,

As far as I know, If you initialized Mcu successfully. This means almost it not come from compiler.

Your problem, clock wasn't provided to ETH correctly. It should come from MCU that you didn't configure correctly or How did you call functions. I looked at your MCU configuration, it seems that has no problem. So, you need to sure that you called functions as below:

I'll ask my team in case you want to organize a debug session. Then, I'll come back to you.

Best regards,

Nhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

fortunately, the problem has been solved. The configuration I sent you I had to do again because I deleted my old environment due to an mistake and with this now it worked. Since I no longer have the old I can not understand what I did differently with the other. But at least it works now and your estimation that it was due to the clock supply was correct.

Now I have another question:

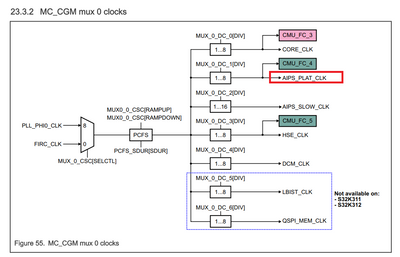

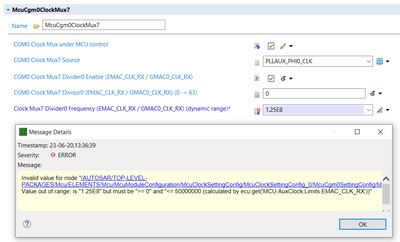

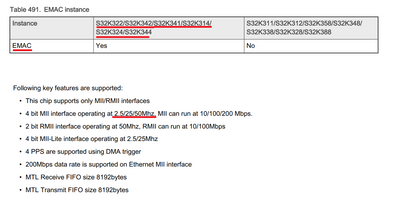

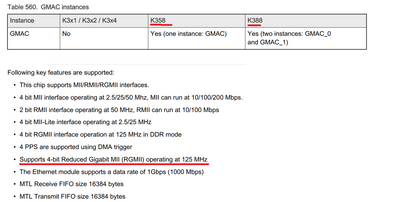

Unfortunately I don't know how to configure the clocking for 4-bit Reduced Gigabit MII (RGMII) operating at 125 MHz, because the MUXes MC_CGM_MUX7-9 (EMAC Clocks RX, TX, TS) only allow 50MHz in the configuration:

Although the S32K358 should support the necessary 125 MHz for the Gigabit range.

As it is descriped I use the PLL_AUX here as clocking source.

Please give me a hint here.

I Thank you very much for your support until now!

BR,

Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi BenjaminKubitschek,

So, maximum clock frequency for EMAC_RX_CLK and EMAC_TX_CLK is 50MHz.

+ For derivatives support GMAC:

So, maximum clock frequency for EMAC_TX_CLK and EMAC_RX_CLK is 125 MHz.

But in Reference Manual, clock diagram just describes for the case EMAC. So, seem that MCU driver is handling maximum frequency clock is similar between GMAC and EMAC (maximum frequency for EMAC_TX_CLK and EMAC_RX_CLK is 50MHz).

At the moment, you can't configure clock 125Mhz through MCU.

I raised this issue to ETH and MCU development team.

Best regards,

Nhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @BenjaminKubitschek,

The GHS Compiler/Linker/Assembler Options can be found in the release notes of the drivers.

For example, optimization level:

Other possibility is that the module is not clocked.

What kind of exception is it?

Bus fault or Usage fault?

Can you read the Configurable Fault Status Register (CSFR) in the handler?

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @danielmartynek,

the deactivation of the compiler optimization brought the execution in the "correct" order, but the exception still appears, so it is not the the problem here.

I do not know which register you men with the CSFR. Is it a special function register or where can I finde it? When I search in the RM for "CSFR" I do not finde a entry. I am still a bit inexperienced with working on hardware and therefore need to have your support again here.

I think the problem here is that a register is loaded which is not initialized. In assembler the code, where the exception appears is:

ldr r2,[r3,#0x00]

in r3 there is the Adress 0x4048500 present, which is the adress of the DMA_MODE register. The debugger isnt able to read the value here with the message "Can not acces target memory".

Is it possible that there is a access lock for this registers? Or is it that this memory space has to be initialized explicitly beforehand?

I think the module is clocked (I am not sure how to prove it). I configured two reference points in the MCU module:

- EMAC_CLK_TS as Module Reference Clock (40 MHz)

- FIRC_CLK as Time Stamp Reference Clock

and referenced them in the eth-module-configuration. I also made sure that the Mcu_InitClock() is called before the init of the ethernet driver.

Thank you for you reply, I hope this additional infos, can help by supporting me. I look forward to an answer

BR,

Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Benny,

Just regarding the register.

CSFR is a register of the core, it is similar to CM4 on S32K1xx:

https://community.nxp.com/t5/S32K-Knowledge-Base/Fault-handling-on-S32K14x/ta-p/1114447

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @danielmartynek,

thank you for reply, I am now able to finde the register-content:

The MMFSR Reg of the CFSR is set here (at 0xE000ED28):

The DACCVIOL and the MMARVALID Flag are set after the exception.

As MMARVALIG is the indicator, that the MMFAR register holds the address which triggered the MemManage fault, I looked for the adress at 0xE000ED34 with the following content:

0x40485000

This also fits with my last message: This is the DMA_MODE register, which I am not able to read with the debugger. So my guess is that this area is not initalized.

How do you see it? What is needed here to solve the problem?

BR,

Benny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @BenjaminKubitschek,

This case has been redirected to the owners of the RTD driver.

Thank you,

BR, Daniel