- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm trying to erase the sector based on the can commands. When I'm trying to erase one of the sector it's not able to erase.

Code structure is Once CAN command comes, it should disable the interrupts and respond the can message and erase the sector and reset the device, so that it can enter the bootloader.

__asm("cpsid i") ;

response_handler(f_info,f_data);

ret=FlashEraseSector(&flashSSDConfig, flash_prog_address, FEATURE_FLS_PF_BLOCK_SECTOR_SIZE, FlashCommandSequence);

if(C90FL_OK != ret)

{

negative_response(f_info,PROGRAM_FAILURE);

}

else

{

asm("nop");

S32_SCB->AIRCR &=0x0000FFFF;

Delay_in_usec(1000000);

// request software reset

S32_SCB->AIRCR = S32_SCB_AIRCR_VECTKEY(0x5FA)| S32_SCB_AIRCR_SYSRESETREQ_MASK;

// wait for reset to occur

while(1);

}

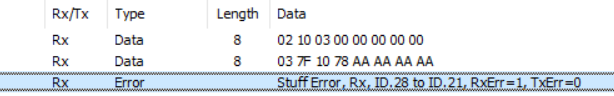

Below is the CAN Error I can see. I can able to see the reset happening as expected but unable to erase the sector though it gives the successfully executes the function FlashEraseSector();

Is there any chance that the program itself resetting while executing FlashEraseSector();

Also, I can able to see the things happen as expected (correctly), with Debug window. But not once programmed.

I also suspect the device, the samples we got were 2 years back & also not the production samples. Can I know how to check the same.

Kindly Help in this regard.

Thanks in advance,

Raju

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Raju,

There could be a reset during the erase command execution.

Please read the RCM_SRS flags after each reset.

This register includes read-only status flags to indicate the source of the most recent reset.

Instead of the the RCM_SRS_SW flag, there could be a LOCKUP.

The ’cpsid i’ instruction sets the PRIMASK special core register, you should be able to read it in the register view.

If you use S32 Design Studio, you can use the ENABLE_INTERRUPTS(), DISABLE_INTERRUPTS() macros (s32_core_cm4.h).

Please locate the function that launches the flash command and make sure that the function is not in PFlash but SRAM/DFlash and the execution stays there until the flash operation is complete.

Thank you,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Raju,

I assume you are using S32K144.

There are three masks 0N77P, ON47T, ON57U (only this one is a production mask), you can read it on the package.

If there is an error during the Erase Flash Sector command execution, you should see one of the errors listed in Table 36-45, RM rev.11. So, I would start with that.

Please make sure that the PFlash block is not read during the flash operation, it would set FTFC Read Collision Error Flag (FSTAT_RDCOLERR).

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

Thanks for your swift response.

First doubt was cleared as we are using FS32K144U AVLH ON57U CTAW1818A & therefore we are production samples only.

Now comes the actual part. I'm dividing the task into 5 parts

1. Disabling interrupts

2. CAN Response

3. Erase Sector

4. Success Message over CAN

5. Reset the Device

Once I receive the CAN command, disable the interrupts, responding to CAN & finally erase the sector and send the success message over CAN then reset the device.

In this I'm able to receive the message, able to disble to interrupts (Step 1), responding to CAN (Step 2), Erase function starts (Step 3) & the device resets and program starts again. I'm not able to see Success Message over CAN (Step 4)

Therefore I suspect that there is a reset happening during erase command. I would like to know the possible cases for the same.

Also is there any chance that __asm("cpsid i") command for disabling Interrupts won't work.

Kindly help in this regard.

Thanks in advance,

Raju.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Raju,

There could be a reset during the erase command execution.

Please read the RCM_SRS flags after each reset.

This register includes read-only status flags to indicate the source of the most recent reset.

Instead of the the RCM_SRS_SW flag, there could be a LOCKUP.

The ’cpsid i’ instruction sets the PRIMASK special core register, you should be able to read it in the register view.

If you use S32 Design Studio, you can use the ENABLE_INTERRUPTS(), DISABLE_INTERRUPTS() macros (s32_core_cm4.h).

Please locate the function that launches the flash command and make sure that the function is not in PFlash but SRAM/DFlash and the execution stays there until the flash operation is complete.

Thank you,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks, Daniel for all the support.

Now everything started working and in fact, I didn't modify anything. And I'm not able to recreate the same situation.

I'll debug the same once the situation occurs again.

Thanks for the support.

Raju