- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K3 DMA

S32K3 DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K3 DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@frank_yang_1 Hi,Frank!

When testing the DMA scatter-gather function , I found the following problems, I hope you can help answer the doubts:

The following buffers are defined in the NoCacheable area.

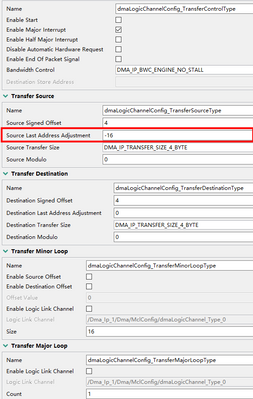

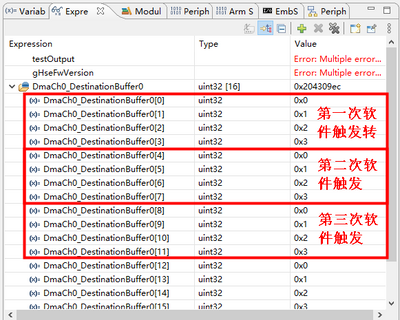

①The configuration S/G channel has only one member, and the software triggers the transfer several times, and the transfer can be carried out normally. The TCD is as follows. After the Major Loop is completed, the source address can be shifted forward by 16Bytes normally.

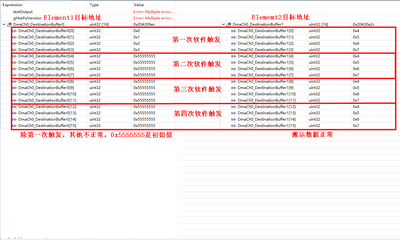

②Add a member on the basis of ①, and the software triggers the transport for mantimey times. Member 2 can be transported normally, and member 1 is only transported normally for the first . The TCD is as follows. After the Major Loop is completed, through the register TCD0_SADDR, it can be seen that member 2 is normal. Offset the source address forward by 16Bytes, but it is not possible to judge whether member 1 is normally offset by looking at the register.

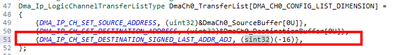

③In addition, it is found that Dma_Ip_Init-> Dma_Ip_LogicChannelInit-> Static_Dma_Ip_SetLogicChannelScatterGatherInit-> HwAccDmaCh_LoadConfigIntoSoftwareTcd will not assign Destination.LastAddrAdj to the register; therefore, after the Major loop is completed, the target address cannot be offset, even if the graphical interface has been configured offset; to achieve address offset Move, you need to manually define it yourself, is this a bug?

The attachment is my routine, if you have time, please help to see if there is any misoperation, thank you very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,zhiwei:

1. When the S/G list has only 1 member, RTD processes it as an DMA normal transfer (i.e. control bit CSR_ESG = 0). And the DMA transfer triggered by Dma_Ip_SetLogicChannelCommand() will use the configuration stored in internal TCD register. The offset after transmission can be normally observed in this case.

2. When the S/G list length is greater than 1, the driver regards it as S/G mode and switches CSR_ESG = 1. In this case, the DMA engine will import the next configuration to the internal TCD register after former transfer complete.

Note:

- Last address adjustment field configured in S32DS_CT is invalid. DMA engine don`t writeback it to external TCD list.

- If user assert INTMAJOR for every S/G list elements, then the number of interruptions may be inconsistent with the number of S/G list. The process of interrupt request to M7_NVIC and the DMA engine process are asynchronous. Then the IRQ handling process maybe slow than DMA engine.

- If the user drive DMA S/G by software codes (i.e. triggering DMA with Dma_Ip_SetLogicChannelCommand), it is necessary to clear the CSR_DONE bit (could do it in DMA interrupt callback) to trigger the next transmission.

- It better to assert INTMAJOR for every DMA S/G elements because the RTD DMA irq driver IrqHandler will check the reg_CSR_INTMAJOR bit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your patience!