- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

S32K144 3-Wire SPI?

Hi,

I'm using S32 Design Studio with S32K144 (with the drivers provided by NXP), how can I use 3-wire SPI on the S32K144 in conjunction with the drivers?

I need to interface with a chip that only provides 3 pins:

* Clock

* Chip Select

* Data Input/Output

Do I need to make any HW Modifications? (e.g. something like this? Interfacing with 3-wire SPI – Total Phase)

Hi,

This protocol is not supported by LPSPI, so if you need to use it you must implement the circuit from figure 2 (with that resistor).

Best regards,

Razvan

Hi Razvan,

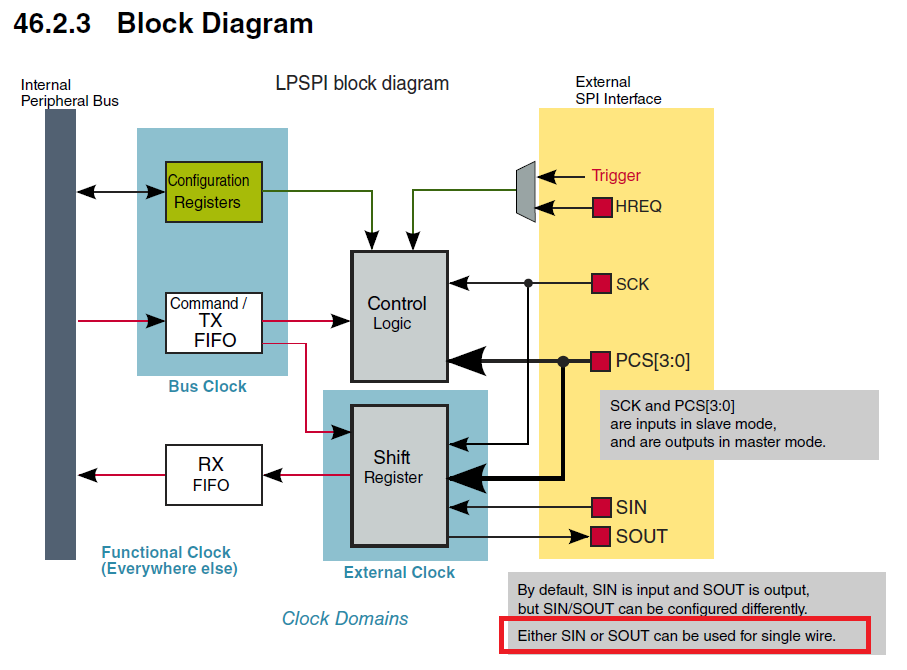

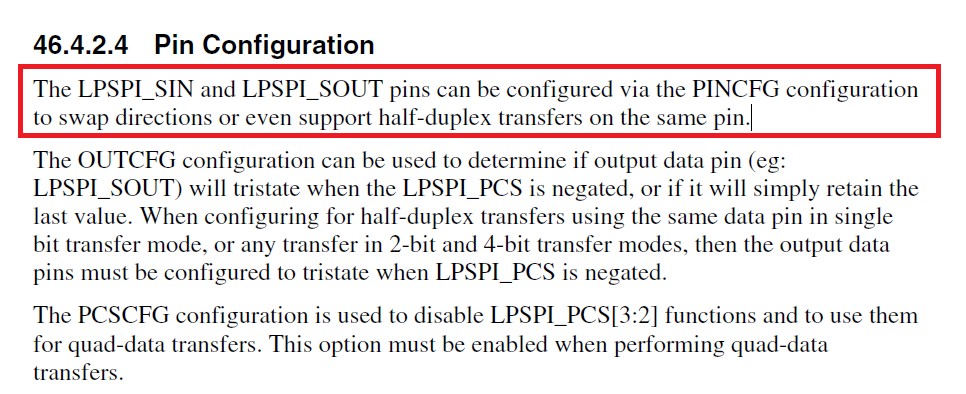

Thank you for replying. Based on the datasheet, the protocol should be supported, although it's called "half-duplex" or "single wire" (see screenshots below), by the way, I wish the datasheet had a section on how to use that mode (what registers to modify with what values) instead of searching all over the chapter for "half-duplex" or "single wire".

I'm trying to use the LPSPI driver provided as part of the S32K SDK, but it seems that it's designed with a full-duplex SPI connection in mind.

I tried the HW modification while calling the LPSPI_DRV_MasterTransferBlocking function but I get whatever was sent on the Rx buffers.

Hi,

Probably the right therm is LPSPI doesn't have "native support" for 3-wire because the work-flow is totally different.

Now, let's get back to your problem.

Please answer to the following questions:

1. what is the frame size in LPSPI configuration?

2. what is the size of the rx/tx in your 3-wire protocol?

3. How do you call LPSPI_DRV_MasterTransferBlocking function?

Best regards,

Razvan

1. I set it up to 8-bit

2. To read from the device: Write 8 bits of register address and then read 8 bits for the value.

3. I tried different ways:

- Sending a TxBuffer and a RxBuffer of 2 bytes each.

- Calling it once to write the address (1 byte) and then calling it again to read the address.

I checked the driver and by default it calls the following function, which means that it's the pins are configured for 2 Data Lines, am I right?

(void)LPSPI_SetPinConfigMode(base, LPSPI_SDI_IN_SDO_OUT, LPSPI_DATA_OUT_RETAINED, true);

Hi,

Please try the following set-up:

Configure the frame size to 16 bit and send with LPSPI_DRV_MasterTransferBlocking 2 bytes.

I suppose that your frame size is 8, so after 8 bits the cs toggle, so your device logic is reset. I think you should keep CS negated during all 16 bits.

Yes, the driver configures the pins for 2 data lines.

Best regards,

Razvan