- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Installing Handler cause "HardFault"

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

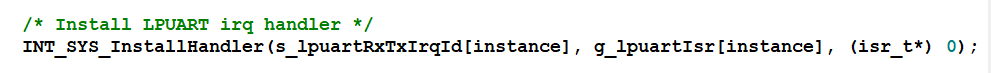

I am Using Keil as S32K IDE,Now I have a problem .EveryTime I want to execute

It will Enter HardFault,I don't know why,because in S32 DS ,The same code works well,Can anybody help me to solve this issue? Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

It looks to me that the interrupt vector is placed in FLASH.

In order to use InstallHandler function the interrupt vector must be placed in RAM.

I currently do not have the linker file for KEIL, but there should be a symbol to place the interrupt vector table in RAM.

Best regards,

Rares

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well...

The Linker file I was working with was the one provided in the SDK for the S32K IDE (S32ds with IAR tool chain): S32K144_64_flash.icf which differs from S32K144_64_ram.icf right in the vector table which is defined in RAM (S32K144_64_ram.icf is provided in the same SDK's example).

In both cases I have the same problem.

I believe that I don't even reach the handler installation because the Hard failure is risen up after the 1st attempt to set up the configuration for the Fault Mode Status (FMS) register of the FTM0.

Below the sequence visualized:

Here's the start up take place:

Then, after the main invocation, there is the initialization of the FTM0 unit...

Inside that function there is a so called "FTM_DRV_Reset" which try the 1st access to the timer...

Inside the very 1st WR operation is a reset of the FMS:

That operation triggers the exception...

According to HFSR is a forced exception, so I checked CFSR = 0x00008200,

The last access was at 0x40038074 (address of "FTM0_FMS").

Using of the wrong linker file is not good. So thanks for the hint...That mistake in any case would be another problem to be fixed for sure.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

It looks like the clock for the FTM instance is not enabled in PCC. This is why it goes to HardFault on the first register access.

Please use clock manager to enable the clock for FTM instance.

Best regards,

Rares

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, The FTM needs the clock settings indeed.

If no set, the initial phase will lead to DefaultISR.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks you a lot mate!!!

It works...

That was the right solution!.

BR.

A.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

Keil Tech Support recommends increasing the Stack and Heap values in startup_xyx.s

They assume your program is running OK until you add this line.

Bob

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

Keil has a similar appnote on fault exceptions:

http://www.keil.com/appnotes/files/apnt209.pdf

Bob

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I got no the solution for your case but I got a way to investigate about the reason of that fault (I'm trying to resolve a similar issue on a project based a IAR tool chain).

Put a break point into the Hard fault handler position (in the ICF file that point is positioned in the start driver "startup_S32K144.s".

When the failure happen the execution should stop there.

Then check HFSR = HardFault Status Register, which should contain the information about what caused the HardFault handler activation.

There are different reasons according to the bit assignments:

b31 - DEBUGEVT: Reserved for debug reasons.

b30 - FORCED: Check the other fault status registers (I think is intended to check the CFSR)

b02 - VECTTBL: All other bits are reserved.

For forther informations you can check the links below:

Configurable Fault Status Register

Let me know if you find a way to get through this because I'm stuck as well.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

You may refer also to

https://community.nxp.com/docs/DOC-334902

I dont use Keil, nor IAR.

Regards,

Daniel

![[S32K] - Re_Installing_Handler_cause_HardFault_1.jpg [S32K] - Re_Installing_Handler_cause_HardFault_1.jpg](/t5/image/serverpage/image-id/4707iC492ED51325FFF59/image-size/large?v=v2&px=999)

![[S32K] - Re_Installing_Handler_cause_HardFault_2.jpg [S32K] - Re_Installing_Handler_cause_HardFault_2.jpg](/t5/image/serverpage/image-id/4750i49822E524DA8F6A5/image-size/large?v=v2&px=999)

![[S32K] - Re_Installing_Handler_cause_HardFault_3.jpg [S32K] - Re_Installing_Handler_cause_HardFault_3.jpg](/t5/image/serverpage/image-id/4799i1DF40A65C4B09C0D/image-size/large?v=v2&px=999)

![[S32K] - Re_Installing_Handler_cause_HardFault_4.jpg [S32K] - Re_Installing_Handler_cause_HardFault_4.jpg](/t5/image/serverpage/image-id/4838i9EF7632F7E452E3B/image-size/large?v=v2&px=999)

![[S32K] - Re_Installing_Handler_cause_HardFault_5.jpg [S32K] - Re_Installing_Handler_cause_HardFault_5.jpg](/t5/image/serverpage/image-id/4865i60C27D987B4A5E79/image-size/large?v=v2&px=999)

![[S32K] - Re_Installing_Handler_cause_HardFault_7.jpg [S32K] - Re_Installing_Handler_cause_HardFault_7.jpg](/t5/image/serverpage/image-id/4912iE363CA5C1F58793B/image-size/large?v=v2&px=999)