- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Could other interrupt influence ADC converter time?

Hi:

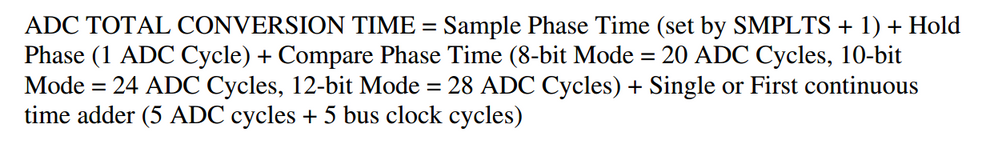

I am using S2K144 ,I can find the total ADC converter time in the RM:

So let's say I calculate total conversion time is 80 bus clock in this way, will the 80 changed to 100 while there is another Interrupt happened and take up 20 bus clock during ADC conversion? Or any other peripherals (such as FLEXCAN LPSPI and so on) able to influence the ADC conversion time?

Hi Feng,

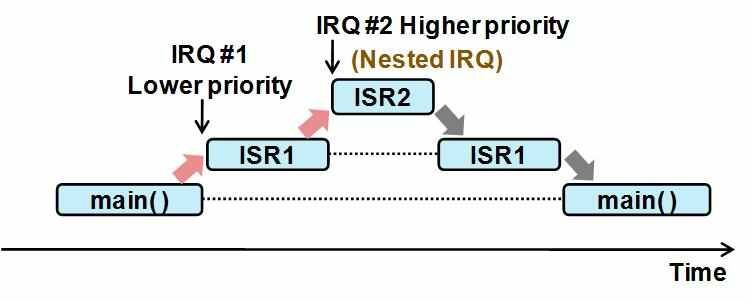

Other peripherals and interrupts will not influence the ADC conversion time.

But higher priority may influence ADC interrupt. You can refer: A Beginner’s Guide on Interrupt Latency - and Interrupt Latency of the Arm Cortex-M processors

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Robin,

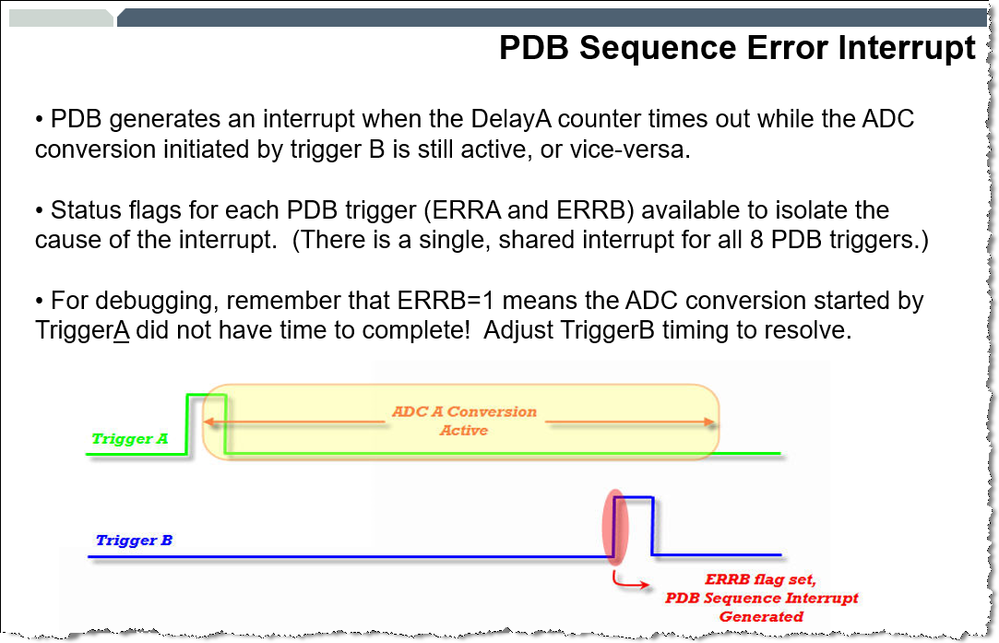

What about use PDB moudle to trigger mulity ADC channel? Each PDB pre-trigger channel'delay is fixed, and they while trigger ADC channel one by one. Could this process be interrupt by Interrupt or other peripherals ?

I mean if I set up PDB1 channel 0 delay 100 bus clock to trigger ADC1 channel 0,and PDB1 channel 1 delay 300 bus clock to trigger ADC1 channel 1, so the ADC1 channel 0 will start conversion at 100 bus clock and end conversion at 180 bus clock, ADC1 channel 1 will start conversion at 300 bus clock and end conversion at 380 bus clock. Is there some case that could make 180 and 380 be other value(such as 200 and 400 or even more)? such as a higher priority interrupt is occurring or some other peripherals is in progress?

Best Regards,

Feng

no.

Are you sure you calculated the ADC total conversion time correctly?

Maybe you can refer the method described in : verify ADC conversion rate with oscilloscope

You should notice the PDB trigger time delay is configured larger than the ADC total conversion time.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Bcause I config some AD channels in my project, I also use some other peripherals (FLEXCAN, LPSPI,LPIT FTM and so on). AD conversion works well(all channels) while there are not some CAN frames on CAN bus. But while there are some CAN frames on the bus(I use interrupt to receive CAN frame in my project), the AD conversion just doesn't work well. It stoped(AD1 channel 0-7) ,But other peripherals seems works well (AD1 channel 8-15 also works well). It confused me a lot.Are there any probabilities?

Best Regards,

Feng

Hi Feng,

I just read another question that you posted: S32K144 DMA Mode Conflict with ADC and CAN

Have you try to reduce the execution time in interrupts?

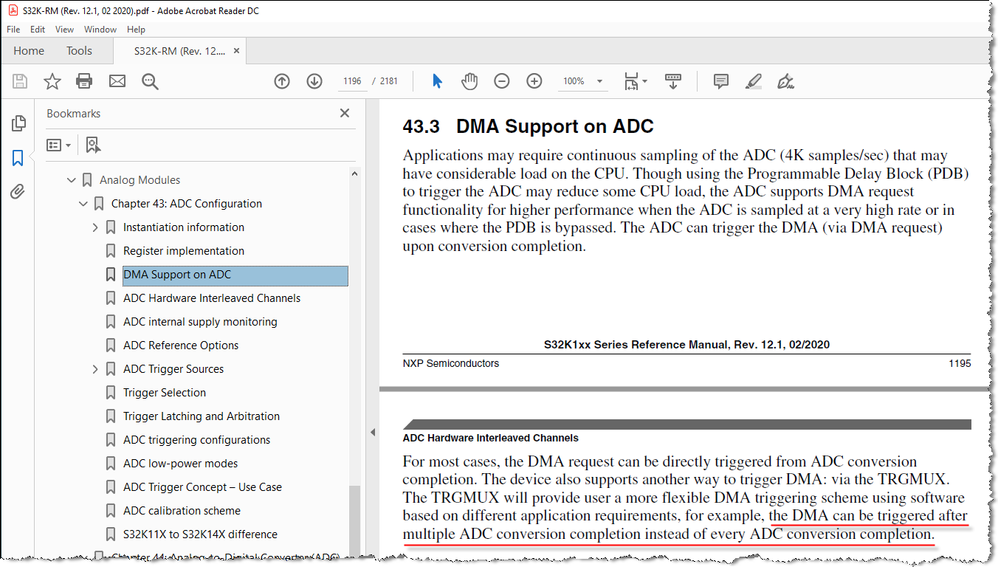

Would you please try to read out all ADC result one time by using DMA in order to reduce the load on the CPU? Seems that your are unable to read ADC result in time by using interrupt, and the ADC interrupt seems influenced by other interrupts.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Actualy, I didnot read AD conversion result in Interrupt or DMA, I read all the results one time. I creat a 10ms task in my project and read all the AD results at the begining of the task ,after I read all the results, I start a new AD conversion by trigger the PDB moudle. And at the next 10ms task running, it kept repeating this process. It seems 120 counter for each PDB channel is enough for AD to complete a conversion while there isnot any CAN message to be received. Isn't it right?

And I changge the PDB counter for each channel to a big number such as 640, seems the AD conversion works well whether there are some messages on the CAN bus to be received. why? It seems there must something influenced by CAN moudle, it make the AD conversion time longer,right? How?

Best Regards,

Feng