- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I operated according to the document of AN13750, but the startup of A core failed (there was no print on the serial port). I hope you can help me provide troubleshooting ideas

My steps are as follows

1.Prepare images for Cortex-A53 cores

- 1:download binaries_auto_linux_bsp33.0_s32g2_pfe.tgz and extract it

- 2:dd if=binaries_auto_linux_bsp33.0_s32g2_pfe/s32g274ardb2/fsl-image-auto-s32g274ardb2.sdcard of=/dev/sdc bs=1M status=progress && sync

- (by this, SD mode startup OK)

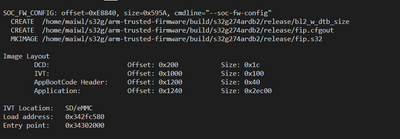

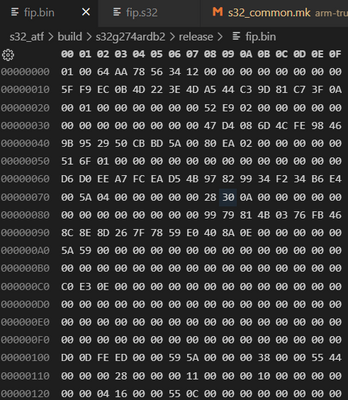

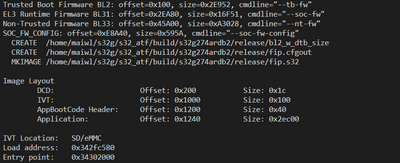

- 5:Build the ATF and got a fip.32 the address info as blow:

- 6:renew fip.32

dd if=fip.s32 of=/dev/sdb skip=512 seek=512 iflag=skip_bytes oflag=seek_bytes conv=fsync,notrunc

- 7:Burn fip.bin to 0x100000

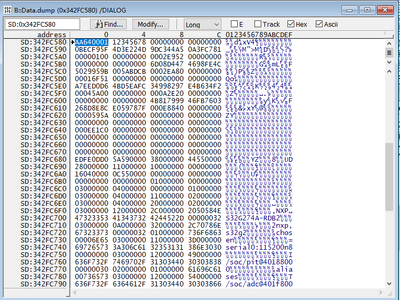

2.Here is the information from Laudbach's debugging

bootloader.c

- main()

- Bl_Run()

- Bl_BootApplications()

- Bl_LoadApplication()

- Bl_FetchApplication()

- Bl_LoadAndAuthFromQspi()

- Bl_StartDmaTransfer()

// Fetch application image and copy to RAM OK

- Bl_StartAllApplications()

- Bl_StartApplication()

// run FIP image(BL2) Failed (no printing information on the serial port)

- Bl_StartApplicationOnCurrentCore()

// run UART sample OK

fip.bin loaded the correct data into the SRAM, but no serial port was printed after execution

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for the information.

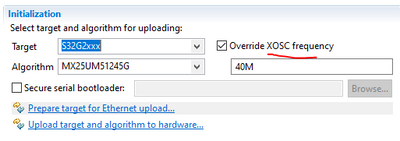

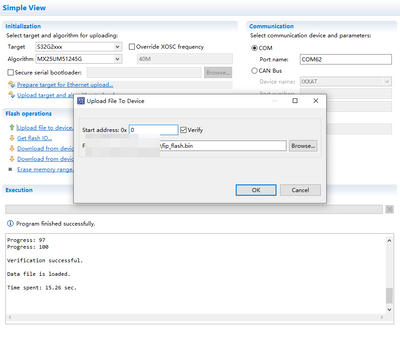

With what you are showing, the only difference we are seeing from our side is the "Override XOSC frequency", which for our setup is enabled as follows:

Aside from this, we are not seeing anything that catches our eyes. Have you flashed a blink example on the NOR Flash? Did it work? For us to know if we jumped a step on this regard.

We could also recommend opening a ticket on the NXP online service, if the situation needs it, the sharing of code or files might be needed, and a more private channel may be recommended.

Please, let us know.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Could you elaborate more on the steps you are following in order to boot the A53 core from the M7? Are you using and NXP board?

We understand the following:

- You overwrite the fip.s32 as explained on the AN13750

- You load the fip.bin to the specified flash address

What we don't understand is how are you setting the M7 bootloader. Did you create the IVT for the M7 with the modified bootloader? Have you changed the boot mode on the board?

Maybe we could recommend a step prior to the M7 bootloader, have you tried to boot the A53_0 from Flash using the fip.bin? To verify you are getting a console output (given that you have confirmed that the SD boot was working).

Please, let us know.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

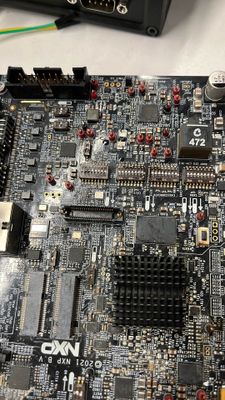

Are you using and NXP board?

Yes, I used the s32g274ardb2

What we don't understand is how are you setting the M7 bootloader. Did you create the IVT for the M7 with the modified bootloader? Have you changed the boot mode on the board?

Yes, I created an IVT image for the Bootloader and set the boot mode to NorFlash

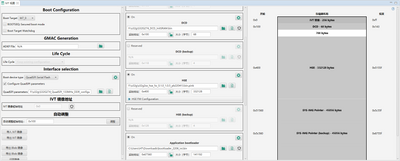

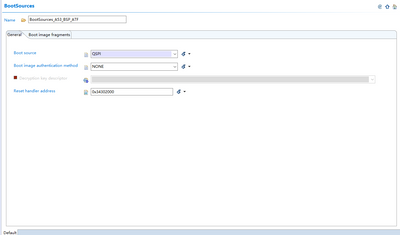

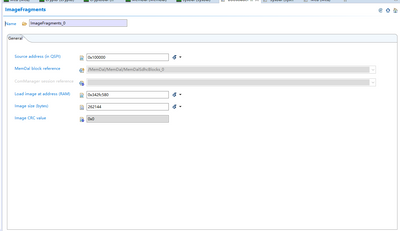

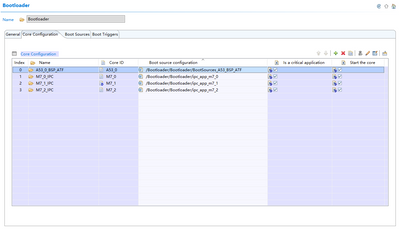

The following figure shows the EB configuration

Uboot Compiled information

have you tried to boot the A53_0 from Flash using the fip.bin? To verify you are getting a console output (given that you have confirmed that the SD boot was working).

SD card startup has been confirmed OK

- I also tried to make an IVT image for fip.bin, burn it to the 0 address of NorFlash, and then load and execute it through BootROM, so as to boot the Uboot. Unfortunately, I failed in this way, and I had no troubleshooting idea for this

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for the information.

Regarding the first part, we are not seeing anything out of the ordinary. Still we will continue looking into your configuration.

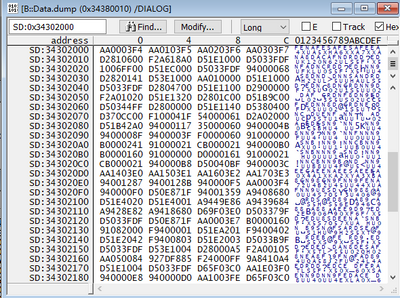

For the second part, we have an RDB2 booting with fip.bin following the below configuration on the IVT:

The address says "app_bl.bin", but it was the name it was given once the "Export Image" button was clicked. It is the "fip.bin" that was loaded in the "Application bootloader" section. Also, the only section that was enabled was "Application bootloader", all of the other sections were disabled.

The Flashing on the NOR Flash was as you are saying, 0x0 as the initial address.

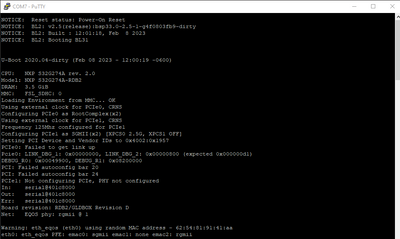

Once the SD is flashed as the AN13750 is showing (with the fip.s32 overwrite) and all the files are put into the root section of the SD (the Image file, the dtb, etc...), we configure the RDB2 boot as NOR Flash (all BOOT_CFG as 0's) and change the boot mode to be from external interface (SW9 0-0, SW10 1-0, meaning that bit 1 on SW10 was on the ON position) we see the booting console on our PC:

With this, we confirm that the fip.bin was generated correctly.

Please, let us know.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

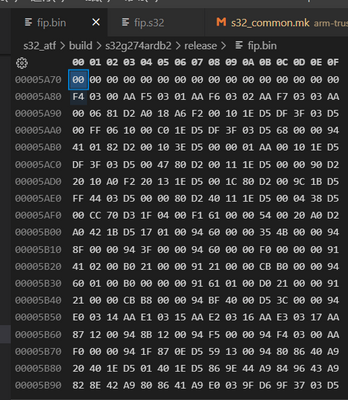

With this, we confirm that the fip.bin was generated correctly.

- The terminal is still not printed and looks like fip.bin is incorrect

The steps of making fip.bin are as follows

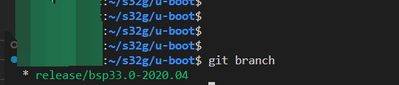

u-boot code branch

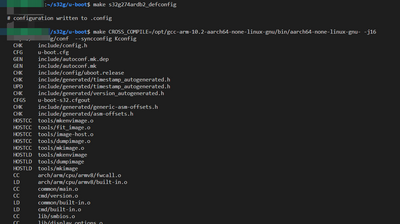

build the U-boot

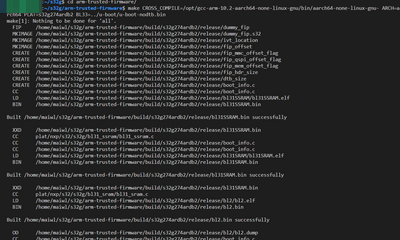

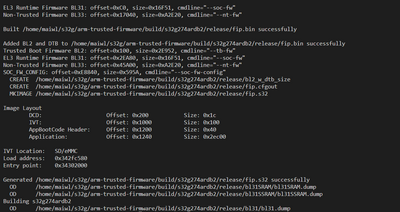

- build ATF

- Create an IVT image

- Burn to Norflash

- boot mode

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for the information.

With what you are showing, the only difference we are seeing from our side is the "Override XOSC frequency", which for our setup is enabled as follows:

Aside from this, we are not seeing anything that catches our eyes. Have you flashed a blink example on the NOR Flash? Did it work? For us to know if we jumped a step on this regard.

We could also recommend opening a ticket on the NXP online service, if the situation needs it, the sharing of code or files might be needed, and a more private channel may be recommended.

Please, let us know.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

如果我没理解错的话,你想在M核启动串口示例,然后再A核启动Linux是吗?

如果是这样,我还是建议你完全按照 AN13750上的来进行(也就是验证他的IPCF通信)

我最初也是想着M核启动串口程序,然后输出一段话,A核同步启动U-boot -> Linux.

但是实际上这里面可能有着资源冲突,比如中断,时钟,端口等,所以这种case无法正常启动

我没有继续调查,然后完全按照 AN13750走了一遍,发现是OK的。

最终,肯定还是要继续调查为什么M和的串口和A核的linux不能同时启动的问题。

NXP似乎没有这样的例子(实际上这样的例子反而更容易让人接收和理解)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

首先感谢你的解答

1.如果我没理解错的话,你想在M核启动串口示例,然后再A核启动Linux是吗?

是的,需求类似这样,M核可能启动其他的应用程序

2.但是实际上这里面可能有着资源冲突,比如中断,时钟,端口等,所以这种case无法正常启动

实际测试中,我先加载A核的BL2(fip.bin)至SRAM中,接着就启动A核了(此时M核还未跳转至APP中运行),这一步也没有跑通,此时应该是还没存在资源冲突的。