- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- Re: S12ZVC SPI Slave without SS ( without CS )

S12ZVC SPI Slave without SS ( without CS )

S12ZVC SPI Slave without SS ( without CS )

Hi,

I want to spare a CS (SS) where my S12ZVC acts as a slave.

Configuration with 1 Master and 1 Slave.

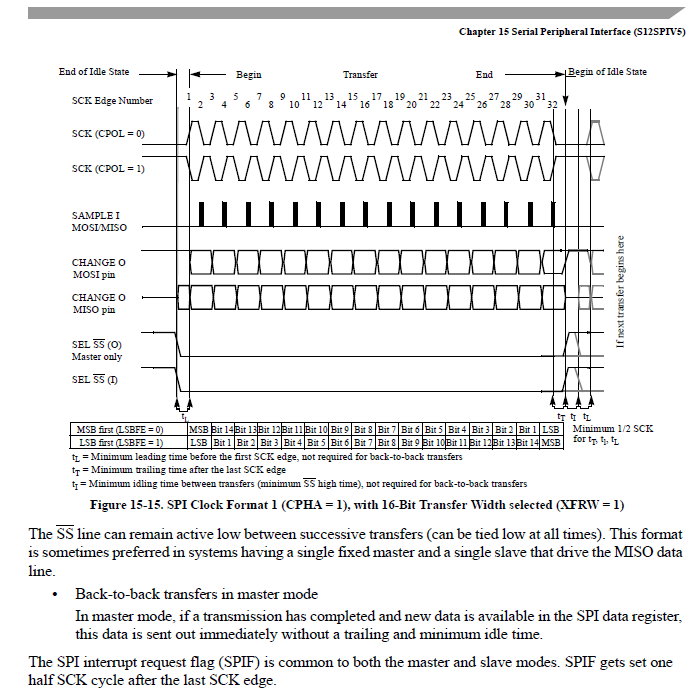

According to Spec 15.4.3.3 CPHA = 1 Transfer Format it is possible, and I pull my Slave´s SS to ground.

"The SS line can remain active low between successive transfers (can be tied low at all times). This format

is sometimes preferred in systems having a single fixed master and a single slave that drive the MISO data

line.

• Back-to-back transfers in master mode

In master mode, if a transmission has completed and new data is available in the SPI data register,

this data is sent out immediately without a trailing and minimum idle time.

The SPI interrupt request flag (SPIF) is common to both the master and slave modes. SPIF gets set one

half SCK cycle after the last SCK edge."

Nevertheless, SPIF interrupt is not occuring. The interrupt SS1_Interrupt comes only once after boot and never again.

Why?

P.S. Pls see in the spec Figure 15-15. SPI Clock Format 1 (CPHA = 1), with 16-Bit Transfer Width selected (XFRW = 1)

Hi,

the SPI bits are not being synchronized properly on SLAVE side without SS.

With SS it is working perfect, but with SS grounded on SLAVE side (SS grounded from beginning of boot) bits are getting mixed up.

It seams like a sync problem.

Master toggles MOSI in red between:

SM1_TComData sendSPIChr1 = 0xFFFF;

SM1_TComData sendSPIChr2 = 0x0000;

Clock is Blue.

SS is green.

MISO is Orange.

WITHOUT SS CONNECTED TO THE SLAVE:

100 values stored in array:

WITH SS CONNECTED TO THE SLAVE:

100 values stored in array:

Did you check with scope what happens on /SS during SPI setup. Isn't master booting up and driving /SS low later than slave initializes? If /SS is disconnected then what about toggling /SS on slave side once after SPI setup, perhaps enabling internal pull up on /SS before initializing SPI, and changing pull direction after SPI initialization?

Edward

Can anyone help here???

I am trying to setup up something your Specification is claiming it works, but I am not getting it working.

We need response fast.

Hi,

/SS is optional on master (SSOE bit), you can't repurpose it for different function on slave! On beasts like iMX, where each pin has its own function select register, perhaps you could, but not on S12ZVC.

Even if you could detach /SS from slave, what about synchronization without SS? You can implement easily something like network SLIP protocol to synchronize at byte level start of the packet, resynchronize in case some byte can be lost. But what about 1st bit synchronization? You loose first edge and... If both slave and master are on the same board and are powered synchronously, then you could configure master and wait say 200ms, while slave powers up and enables SPI perhaps 100ms after power on. This would kind of provide 1st bit synchronization.. But you still would need to have some I'm alive and not silly checks on both master and slave. Once happens, disable master SPI activity say for 200ms, disable SPI on slave, use port interrupt to detect master is idle say > 100ms, then reenable SPI...

Edward

Hi Edward,

thanks for your response.

Actually, I dont want to repurpose SS. I want to SPI with 3 lines, so I save 1 line.

So spec. says this is possible with CPHA = 1:

and that is what I want to do.

Now, if I understood your 2nd paragraph, your concern is regarding initial synchronization. Currently, I am testing this with 2 Hearst devel boards, so I can force SPI Slave to run first, then I turn on the SPI Master, therefore initial sync should not be a problem.

Nevertheless, SPI Slave is not receiving properly nor responding.

P.S. tL is minimum leading time, therefore can be greater, and that is the case in my start procedure; it is also not required in back-to-back.

Haven´t tried 8 bit, but it should also work in 16 bit, according to spec.

I am using the interrupt from ProcessorExpert:

ISR(SS1_Interrupt)

{

SS1_TComData Data = 0U; /* Temporary variable for data */

byte Flags = 0U; /* Temporary variable for flags */

if (SPI0SR_SPIF) { /* Occured any Rx interrupt condition? */

if(SPI0SR_SPIF){SPI1SR_SPIF_status += 1;}

Data = SPI0DR; /* Read data from receiver */

Flags |= ON_RX_CHAR_EXT; /* Set the OnRxCharExt flag */

if (SerFlag & CHAR_IN_RX) { /* Is the overrun error flag set? */

SerFlag |= OVERRUN_ERR; /* If yes then set the Overrun error flag */

Flags |= ON_ERROR; /* If yes then set the OnError flag */

ErrFlag |= OVERRUN_ERR; /* Set error flag for GetError method */

}

SerFlag |= CHAR_IN_RX; /* Set flag "char in RX buffer" */

BufferRead = Data; /* Read data from receiver */

Flags |= ON_RX_CHAR; /* If yes then set the OnRxChar flag */

}

SPI0CR1_SPTIE = 0U; /* Disable transmit interrupt */

if (SPI0SR_SPTEF) { /* Is the transmit buffer empty? */

if (SerFlag & FULL_TX) { /* Is "Full TX buffer" flag set? */

SPI0DR = BufferWrite; /* If yes then store char to the transmit register */

Flags |= ON_TX_CHAR; /* Set the OnTxChar flag */

SerFlag &= (byte)(~(byte)FULL_TX); /* Reset flag "Full TX buffer" */

} else {

SPI0DR = SS1_EOF; /* If no then store the empty char to the transmit register */

Flags |= ON_EMPTY_CHAR; /* Set the OnTxEmptyChar flag */

}

}

if(SS1_EnEvent) { /* Are the events enabled? */

if (Flags & ON_RX_CHAR_EXT) { /* Is OnRxCharExt flag set? */

SS1_OnRxCharExt(Data); /* If yes then invoke user event */

}

if (Flags & ON_ERROR) { /* Is any error flag set? */

__DI();

SS1_OnError(); /* If yes then invoke user event */

} else {

if (Flags & ON_RX_CHAR) { /* Is OnRxChar flag set? */

__DI();

SS1_OnRxChar(); /* If yes then invoke user event */

}

}

if (Flags & ON_TX_CHAR) { /* Is OnTxChar flag set? */

__DI();

SS1_OnTxChar(); /* If yes then invoke user event */

}

if (Flags & ON_EMPTY_CHAR) { /* Is OnTxEmptyChar flag set? */

__DI();

SS1_OnTxEmptyChar(); /* If yes then invoke user event */

}

}

}

and added in the:

void SS1_OnRxChar(void)

{

/* Write your code here ... */

statusSPIReceive = SS1_RecvChar(&charSlaveReceiveSPI);

statusSPISend = SS1_SendChar(sendSPIChr);

if (sendSPIChr == sendSPIChr1){

sendSPIChr = sendSPIChr2;

}

else if (sendSPIChr == sendSPIChr2){

sendSPIChr = sendSPIChr1;

}

else {

sendSPIChr = 0xAAAA;

}

}

OK, I found out what is the problem :-)

SPI CLK line was broken. :-)

I am getting though response from the slave which is not very logical (see above) for the constant slave message:

0b0101010101010101

P.S. I am measuring with an oscilloscope and messages from the master are fine.

Though, when I pull slave´s SS to ground, it´s MISO goes to unsteady -10mV, otherwise without pull of SS to ground it is on steady 1,18V.