- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- Re: 9S12E256

9S12E256

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

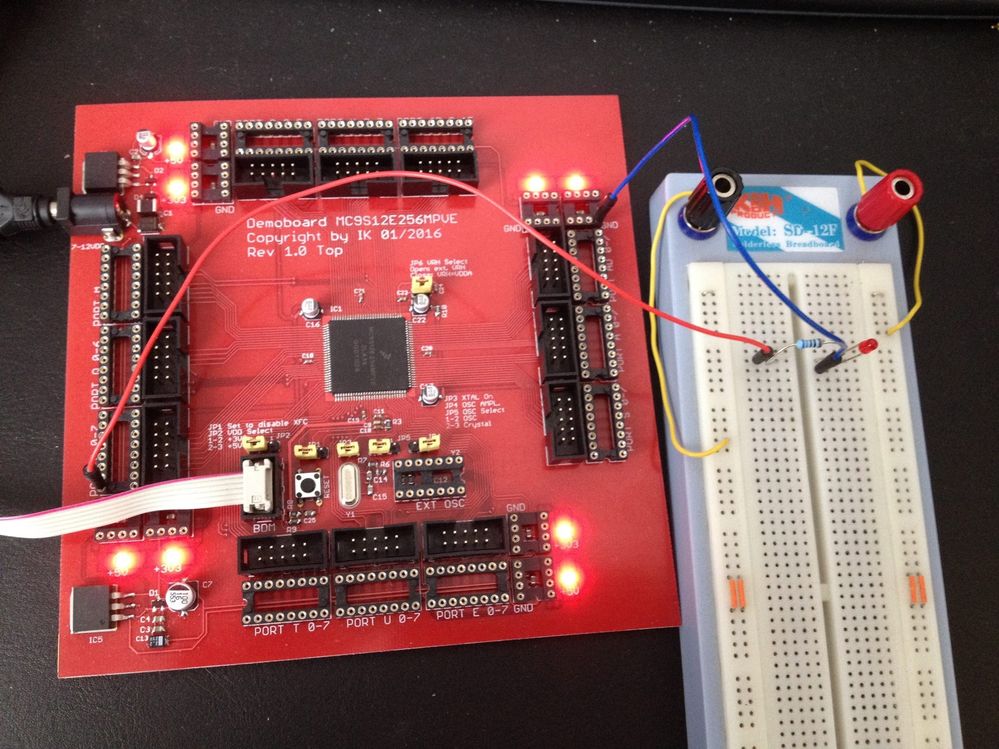

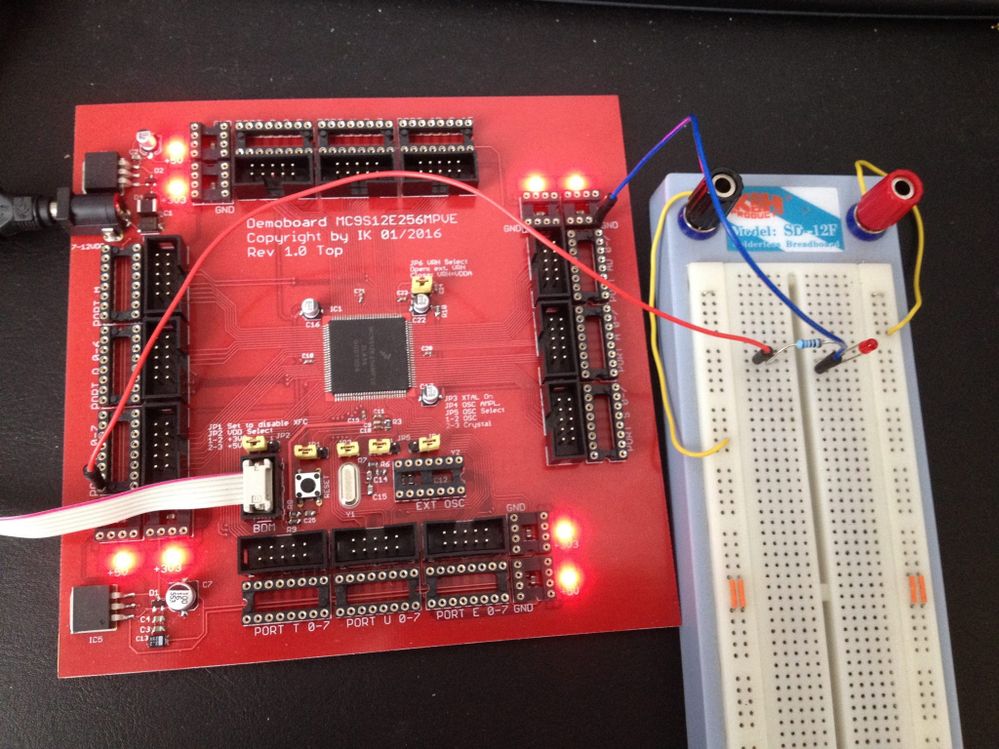

I´ve made this board below and I have testet the IO with the following code on each port (I used different Register names for each port):

LDAA #$00FF

STAA DDRB

Main:

LDAA #$00FF

STAA PORTB

JSR DELAY

LDAA #$0000

STAA PORTB

JSR DELAY

BRA Main

This works great but If I use bset or bclr instruction then it does not work. I am not able to toggle the led on my breadboard with the following code.)

Example:

BSET 0, DDRB ;also tried BSET DDRB, %00000001 without success and also the rest of the code in that way without success

Main:

BSET 0,PORTB

JSR DELAY

BCLR 0,PORTB

JSR DELAY

BRA Main

Can anyone help me?

I have to say, I am new to the 16Bit HCS MCU´s but I have a good knowledge on the HCS08. I always write my code in Assembly language.

-BR Ingo

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

BSET DDRA, #0xFF will set all DDRA bits. HC08/S08 BSET instruction can set single bit, while S12 takes bit mask.

BSET 0, DDRA will probably set bit1 (DDRA address is 2, which is bitmask of bit1) of byte @0 (PORTA is at 0). Though it shouldn't even compile (in the right compiler), since immediate addressing requires # sign.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

An example, for D32 in the CodeWarrior. You can find there also BSET and BCL instructions format.

;*******************************************************************************

;* Freescale Semiconductor Inc.

;* (c) Copyright 2004-2005 Freescale Semiconductor, Inc.

;* ALL RIGHTS RESERVED.

;*******************************************************************************

;Services performed by FREESCALE in this matter are performed AS IS and without

;any warranty. CUSTOMER retains the final decision relative to the total design

;and functionality of the end product. FREESCALE neither guarantees nor will be

;held liable by CUSTOMER for the success of this project.

;FREESCALE DISCLAIMS ALL WARRANTIES, EXPRESSED, IMPLIED OR STATUTORY INCLUDING,

;BUT NOT LIMITED TO, IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR

;A PARTICULAR PURPOSE ON ANY HARDWARE, SOFTWARE OR ADVISE SUPPLIED TO THE PROJECT

;BY FREESCALE, AND OR NAY PRODUCT RESULTING FROM FREESCALE SERVICES. IN NO EVENT

;SHALL FREESCALE BE LIABLE FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF

;THIS AGREEMENT.

;

;CUSTOMER agrees to hold FREESCALE harmless against any and all claims demands or

;actions by anyone on account of any damage, or injury, whether commercial,

;contractual, or tortuous, rising directly or indirectly as a result of an advise

;or assistance supplied CUSTOMER in connection with product, services or goods

;supplied under this Agreement.

;*******************************************************************************

;* File main.c

;* Owner Ladislav

;* Version 1.0

;* Date Oct-4-2014

;* Classification General Business Information

;* Brief Test 8x8 CAN filter in loopback mode

;*******************************************************************************

; TECHNICAL SUPPORT - SOFTWARE EXAMPLE

;*******************************************************************************

;* Detailed Description:

;*

; - CAN0 in loopback mode

; - bitrate 250kbps

; - Used OSCCLK = 16MHz BUSCLK=8MHz, CANCLK derived from OSCCLK (recommended)

;

; The SW:

; 1) CAN0 Tx in polling mode CAN0 Rx is set for interrupt mode

;

; 2) Extended identifier is used only for Tx and Rx(filter)

;

; 3) Filters filter and accept all extended IDs only. Standard IDs are

; filtered out

; - tested on: EVB Softec ZK-S12-A

; - OSCCLK = 16MHz oscillator, BUSCLK = 8MHz

;*******************************************************************************

;Revision History:

;Version Date Author Description of Changes

;1.0 Oct-4-2014 Ladislav Initial version

; ******************************************************************************

; Include derivative-specific definitions

INCLUDE 'derivative.inc'

; export symbols

XDEF Entry, _Startup, main, CAN0RXISR

; we use export 'Entry' as symbol. This allows us to

; reference 'Entry' either in the linker .prm file

; or from C/C++ later on

XREF __SEG_END_SSTACK ; symbol defined by the linker for the end of the stack

;@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@

; variable/data section

MY_EXTENDED_RAM: SECTION

; Insert here your data definition.

;extended ID structure

;0x00X0 IDR0 - ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21

;0x00X1 IDR1 - ID20 ID19 ID18 SRR(=1) IDE(=1) ID17 ID16 ID15

;0x00X2 IDR2 - ID14 ID13 ID12 ID11 ID10 ID9 ID8 ID7

;0x00X3 IDR3 - ID6 ID5 ID4 ID3 ID2 ID1 ID0 RTR

RXmsgID0 ds.b 1 ;

RXmsgID1 ds.b 1 ;

RXmsgID2 ds.b 1 ;

RXmsgID3 ds.b 1 ;

RXmsglen ds.b 1 ;

RXmsgdata0 ds.b 1

RXmsgdata1 ds.b 1

RXmsgdata2 ds.b 1

RXmsgdata3 ds.b 1

RXmsgdata4 ds.b 1

RXmsgdata5 ds.b 1

RXmsgdata6 ds.b 1

RXmsgdata7 ds.b 1

TXmsgID0 ds.b 1 ;

TXmsgID1 ds.b 1 ;

TXmsgID2 ds.b 1 ;

TXmsgID3 ds.b 1 ;

TXmsgprty ds.b 1 ;

TXmsglen ds.b 1 ;

TXmsgdata0 ds.b 1

TXmsgdata1 ds.b 1

TXmsgdata2 ds.b 1

TXmsgdata3 ds.b 1

TXmsgdata4 ds.b 1

TXmsgdata5 ds.b 1

TXmsgdata6 ds.b 1

TXmsgdata7 ds.b 1

data ds.b 1

tx_free_buf ds.b 1

;@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@

; code section

MyCode: SECTION

main:

_Startup:

Entry:

LDS #__SEG_END_SSTACK ; initialize the stack pointer

;--------------------------

;data=1;

MOVB #1, data

;PEAR_NECLK = 0;

BCLR PEAR,#$10

;init CAN

;250 kbps, 1sample/bit, 16MHz ext osc as CAN clock source, loop disabled

;CAN interface (PCA82C250)

;init_CAN(0xC3, 0x67, CAN0CTL1_CANE_MASK | CAN0CTL1_LOOPB_MASK);

;CAN0CTL0 = CAN0CTL0_INITRQ_MASK;

MOVB #1, CAN0CTL0

;while(!(CAN0CTL1 & CAN0CTL1_INITAK_MASK));

BRCLR CAN0CTL1,#1,*+0

;CAN0CTL1 = CAN0CTL1_CANE_MASK | CAN0CTL1_LOOPB_MASK;

;Enables MSCAN, Oscillator Clock, Loop Enabled/Disabled and Normal Operation

MOVB #$A0,CAN0CTL1

;CAN0BTR0 = 0xC3;

MOVB #$C3, CAN0BTR0

;CAN0BTR1 = 0x67;

MOVB #$67, CAN0BTR1

;CAN0IDAC = 0x10; // CAN Filter 4x16

MOVB #$10, CAN0IDAC

; ACCEPT ALL EXTENDED IDs

; 16b CAN Filter scheme for extended identifier

; ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21

; ID20 ID19 ID18 SRR(=1) IDE(=1) ID17 ID16 ID15

;CAN0IDAR0_CAN0IDAR1 = 0x0008; // extended ID flag

MOVW #$0018, CAN0IDAR0 ; SRR=1, IDE=1

;CAN0IDMR0_CAN0IDMR1 = 0xFFE7; // accept extended identifiers only

MOVW #$FFE7,CAN0IDMR0 ; check SRR and IDE

;CAN0IDAR2_CAN0IDAR3 = 0x0008; // extended ID flag

MOVW #$0018, CAN0IDAR2 ; SRR=1, IDE=1

;CAN0IDMR2_CAN0IDMR3 = 0xFFE7; // accept extended identifiers only

MOVW #$FFE7,CAN0IDMR2 ; check SRR and IDE

;CAN0IDAR4_CAN0IDAR5 = 0x0008; // extended ID flag

MOVW #$0018, CAN0IDAR4 ; SRR=1, IDE=1

;CAN0IDMR4_CAN0IDMR5 = 0xFFE7; // accept extended identifiers only

MOVW #$FFE7,CAN0IDMR4 ; check SRR and IDE

;CAN0IDAR6_CAN0IDAR7 = 0x0008; // extended ID flag

MOVW #$0018, CAN0IDAR6 ; SRR=1, IDE=1

;CAN0IDMR6_CAN0IDMR7 = 0xFFE7; // accept extended identifiers only

MOVW #$FFE7,CAN0IDMR6 ; check SRR and IDE

;CAN0TL0 = 0x00; // restart MSCAN peripheral

CLR CAN0CTL0

;while(CAN0CTL1_INITAK); // wait for Initialization Mode exit

BRSET CAN0CTL1,#1,*+0

;while(!CAN0CTL0_SYNCH); // waits for MSCAN synchronization with the CAN bus

BRCLR CAN0CTL0,#16,*+0

;CAN0RIER_RXFIE = 1; // enable can 0 Rx interrupt

BSET CAN0RIER,#1

;EnableInterrupts;

CLI

;---------------------------------------

EndlessLoop:

;--- prepare CAN Tx frame ---

;TXmsgID = 0x12183456; only example but SRR and IDE must be 1 for extended ID

;extended ID structure

;IDR0 - ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21

;IDR1 - ID20 ID19 ID18 SRR(=1) IDE(=1) ID17 ID16 ID15

;IDR2 - ID14 ID13 ID12 ID11 ID10 ID9 ID8 ID7

;IDR3 - ID6 ID5 ID4 ID3 ID2 ID1 ID0 RTR

MOVB #$12,TXmsgID0

MOVB #$18,TXmsgID1 ; SRR=1, IDE=1

MOVB #$34,TXmsgID2

MOVB #$56,TXmsgID3

;TXmsglen = 8;

MOVB #8,TXmsglen

;TXmsgprty= 3;

MOVB #3,TXmsgprty

;TXmsgdata0_7= data++;

LDAB data

STAB TXmsgdata0

INCB

STAB TXmsgdata1

INCB

STAB TXmsgdata2

INCB

STAB TXmsgdata3

INCB

STAB TXmsgdata4

INCB

STAB TXmsgdata5

INCB

STAB TXmsgdata6

INCB

STAB TXmsgdata7

INCB

STAB data

;---use prepared data and fill can registers ---

;find free Tx buffer

;tx_free_buf = 0;

CLR tx_free_buf

;while(!(CAN0TFLG & (0x01<<tbuf_n_empty_flag))) // find empty transmit buffer from 3 buffers

MAINLBL2:

MOVB #1, tx_free_buf

BRSET CAN0TFLG,#1,MAINLBL1

MOVB #2, tx_free_buf

BRSET CAN0TFLG,#2,MAINLBL1

MOVB #4, tx_free_buf

BRSET CAN0TFLG,#4,MAINLBL1

JMP MAINLBL2

MAINLBL1:

;CAN0TBSEL = 0x01 << tbuf_n_empty_flag; // select found empty transmit buffer

MOVB tx_free_buf,CAN0TBSEL

;fill Tx ID

MOVB TXmsgID0,CAN0TXIDR0

MOVB TXmsgID1,CAN0TXIDR1

MOVB TXmsgID2,CAN0TXIDR2

MOVB TXmsgID3,CAN0TXIDR3

;fill Tx data buffers

MOVB TXmsgdata0,CAN0TXDSR0

MOVB TXmsgdata1,CAN0TXDSR1

MOVB TXmsgdata2,CAN0TXDSR2

MOVB TXmsgdata3,CAN0TXDSR3

MOVB TXmsgdata4,CAN0TXDSR4

MOVB TXmsgdata5,CAN0TXDSR5

MOVB TXmsgdata6,CAN0TXDSR6

MOVB TXmsgdata7,CAN0TXDSR7

;CAN0TXDLR = TXmsglen; // set message data length

MOVB TXmsglen, CAN0TXDLR

;CAN0TXTBPR = TXmsgprty; // set message internal priority

MOVB TXmsgprty, CAN0TXTBPR

;CAN0TFLG = (0x01<<tbuf_n_empty_flag); // clear flag to send message

MOVB tx_free_buf,CAN0TFLG

;-------------------------

BSR DELAY

;-------------------------

JMP EndlessLoop ; restart.

;"""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""

DELAY:

;"""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""

;for(i=0;i<0x05;i++) for(j=0;j<0xFFFF;j++) { asm nop; }

PSHD

PSHX

LDD #5

DELAYLBL1:

LDX #$FFFF

DELAYLBL2:

NOP

DBNE X,DELAYLBL2

DBNE D,DELAYLBL1

PULX

PULD

RTS

;"""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""

CAN0RXISR: ; here is one of possible approaches to connect interrupt vector

; with label(address)

; 1) see export symbols on the top of this page

; 2) see vector definition in the Project.prm file (bottom):

; VECTOR 38 CAN0RXISR

;

;"""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""""

MOVB CAN0RXIDR0,RXmsgID0

MOVB CAN0RXIDR1,RXmsgID1

MOVB CAN0RXIDR2,RXmsgID2

MOVB CAN0RXIDR3,RXmsgID3

;RXmsglen = CAN0RXDLR & 0x0F;

LDAB CAN0RXDLR

ANDB #15

STAB RXmsglen

;RXmsgdata0_7 = CAN0RXDSR0_7;

MOVB CAN0RXDSR0,RXmsgdata0

MOVB CAN0RXDSR1,RXmsgdata1

MOVB CAN0RXDSR2,RXmsgdata2

MOVB CAN0RXDSR3,RXmsgdata3

MOVB CAN0RXDSR4,RXmsgdata4

MOVB CAN0RXDSR5,RXmsgdata5

MOVB CAN0RXDSR6,RXmsgdata6

MOVB CAN0RXDSR7,RXmsgdata7

;CAN0RFLG = CAN0RFLG_RXF_MASK; // clear flag

MOVB #1,CAN0RFLG

RTI

;@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@

Best regards,

Ladislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your help!

I am sorry, I was so blind and could´nt see that

BSET PORTB,mDDRB_BIT7

BCLR PORTB,mDDRB_BIT7

works perfectly for me!

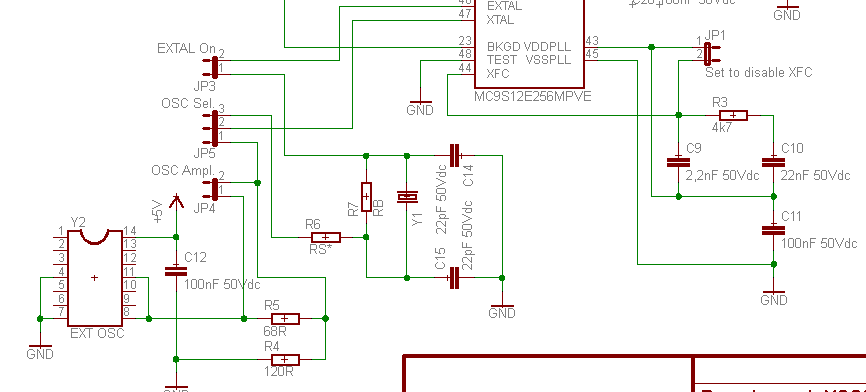

Now I am trying to determine the Busclock with an Frequency Counter. Pin PE7 is tied to ground (Pierce Oscillator 16Mhz 2pcs. 22pF).

Everything I am trying Ends up with a 137khz Busclock and I dont know how to fix it.

This is my schematic:

Can anyone help me out? I would like to have a 8Mhz or 16 Mhz busclock.

BR

-Ingo

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

the PLL components you use are the most suitable for PLL setup with Synr=refdv=10 when you want to make 16MHz busclk from a S12 MHz oscclk. I suppose you have used correct load capacitance for used oscillator.

E256 : input pin capacitance for pins XTAL, EXTAL C1i = C2i = 7pF = Ci

Let C3=C4 = Ce

CLoad = (Ci + Ce)/2 and it has to be >= CLoad = 10 pF Cload is taken from a datashett for given oscillator, in this example 10pF

Then:

(Ci + Ce)/2 >= CL => Ce >= CL*2 - Ci

Ce >= 10pF * 2 - 7pF

Ce >= 13 pF

Rb value is from the interval 100kohm ~ 20Mohm. For low frequency circuits is crystal impedance relatively high and Rb should be high Rb = 10Mohm. For high frequencies (>20Mhz) Rb = 100 kohm.

Rs for high frequencies (>4MHz) can be omitted.

Moreover I suppose that you have only 100nF capacitors between Vdd and Vss because some customers connected Vdd to 5V which is mistake. May I see entire environment of the MCU?

Simple example of PLL setup:

static void PLL_Init(void)

{

CLKSEL &= 0x7F; // set BUS CLOCK 16MHz from 16MHz MHz OSCCLK

REFDV = 0;

SYNR = 0;

while(!(CRGFLG_LOCK));

CLKSEL_PLLSEL = 1;

PEAR_NECLK = 0; // make BUSCLK visible at PE4 pin

}

Have you measure frequency at oscillator to be sure it is working?

I hope you do not have any wire nor ground plane under oscillator circuitry. It can affect the oscillator in the way it is not working.

I would like to ask you, in the future, to create a new question at community if it does not corresponds to previous question.

Best regrads,

Ladislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

BSET DDRA, #0xFF will set all DDRA bits. HC08/S08 BSET instruction can set single bit, while S12 takes bit mask.

BSET 0, DDRA will probably set bit1 (DDRA address is 2, which is bitmask of bit1) of byte @0 (PORTA is at 0). Though it shouldn't even compile (in the right compiler), since immediate addressing requires # sign.