- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 移动机器人 - 无人机和漫游者

- :

- 机器人硬件

- :

- Re: RDDRONE-BMS772

RDDRONE-BMS772

RDDRONE-BMS772

Please ask questions about the RDDRONE-BMS772 board and software here

Thank you for your answer,

I already tried with the J2 connector(it is placed) thought JTAG lines, with the reset jumper and without it. And I still cannot connect to the target.

What could I do? How could I check the Reset line is properly connected and the signal is ok.

Thank you very much @cisvmierlo

Hi,

I have a problem with the RDDRONE-BMS772 board.

I soldered the hardware "configuration pads" as recommended in the RDDRONE-BMS772 manual for a 6s battery.

Then, I connected the RDDRONE-BMS772 board to a 22.2V power supply for the first time, the onboard LED turned on.

I followed the steps in this guide from the "NXP Gitbook":

https://nxp.gitbook.io/nxpmobilerobotics/flashing-guide/flashing-hovergames-boards/windows

but after trying to flash the firmware bin file downloaded from the official github:

https://github.com/NXPHoverGames/RDDRONE-BMS772

with the recommended J-LINK debugger and I connected the cables as seen here:

The flash failed (log below), and I cannot connect to the RDDRONE-BMS772 board anymore. Furthermore, the LED does not turn on either. I am trying to re-flash it, but I cannot get J-Link commander to connect to the RDDRONE-BMS772 anymore.

If I try to access the board using an FTDI cable, I do not get any serial connection using Putty either.

I am a bit confused as I do not understand if the problem is that the CPU is halted, or the CPU is in a RESET loop, the CPU waiting for a RESET signal, the CPU is "locked" and I have to unlock it, or if it is something else.

Any help would be highly appreciated.

This is the log I got from the J-Link Commander console, in case it is helpful:

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: S32K144

Type '?' for selection dialog

Device>

Please specify target interface:

J) JTAG (Default)

S) SWD

T) cJTAG

TIF>s

Specify target interface speed [kHz]. <Default>: 4000 kHz

Speed>1000

Device "S32K144" selected.

Connecting to target via SWD

InitTarget() start

SWD selected. Executing JTAG -> SWD switching sequence.

InitTarget() end - Took 55ms

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

Scanning AP map to find all available APs

AP[2]: Stopped AP scan as end of AP map has been reached

AP[0]: AHB-AP (IDR: 0x24770011)

AP[1]: JTAG-AP (IDR: 0x001C0000)

Iterating through AP map to find AHB-AP to use

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE00FF000

CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

Found Cortex-M4 r0p1, Little endian.

FPUnit: 6 code (BP) slots and 2 literal slots

CoreSight components:

ROMTbl[0] @ E00FF000

[0][0]: E000E000 CID B105E00D PID 000BB00C SCS-M7

[0][1]: E0001000 CID B105E00D PID 003BB002 DWT

[0][2]: E0002000 CID B105E00D PID 002BB003 FPB

[0][3]: E0000000 CID B105E00D PID 003BB001 ITM

[0][4]: E0040000 CID B105900D PID 000BB9A1 TPIU

Initializing 61440 bytes work RAM @ 0x1FFF8000

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.SYSRESETREQ.

Memory zones:

Zone: "Default" Description: Default access mode

Cortex-M4 identified.

J-Link>erase

No address range specified, 'Erase Chip' will be executed

'erase': Performing implicit reset & halt of MCU.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.SYSRESETREQ.

Erasing device...

****** Error: Failed to erase sectors.

J-Link: Flash download: Total time needed: 1.490s (Prepare: 0.603s, Compare: 0.000s, Erase: 0.885s, Program: 0.000s, Verify: 0.000s, Restore: 0.002s)

****** Error: Failed to restore target. RAMCode never stops

ERROR: Erase returned with error code -5.

J-Link>loadbin "C:\Documents\RDDRONE-BMS772-main\Binary\nuttx.bin" 0x0

'loadbin': Performing implicit reset & halt of MCU.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.SYSRESETREQ.

Reset: SYSRESETREQ has confused core.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

Reset: Using fallback: VECTRESET.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.VECTRESET.

Reset: VECTRESET has confused core.

Reset: Using fallback: Reset pin.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via reset pin

Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Reset: Reconnecting and manually halting CPU.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

CPU could not be halted

Reset: Core did not halt after reset, trying to disable WDT.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via reset pin

Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Reset: Reconnecting and manually halting CPU.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

CPU could not be halted

Reset: Failed. Toggling reset pin and trying reset strategy again.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.SYSRESETREQ.

Reset: SYSRESETREQ has confused core.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

Reset: Using fallback: VECTRESET.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.VECTRESET.

Reset: VECTRESET has confused core.

Reset: Using fallback: Reset pin.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via reset pin

Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Reset: Reconnecting and manually halting CPU.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

CPU could not be halted

Reset: Core did not halt after reset, trying to disable WDT.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via reset pin

Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Reset: Reconnecting and manually halting CPU.

Found SW-DP with ID 0x2BA01477

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Attach to CPU failed. Executing connect under reset.

DPIDR: 0x2BA01477

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Skipped. Could not read CPUID register

Could not find core in Coresight setup

CPU could not be halted

CPU could not be halted

****** Error: Failed to halt CPU.

CPU could not be halted

Downloading file [C:\Documents\RDDRONE-BMS772-main\Binary\nuttx.bin]...

CPU could not be halted

****** Error: Failed to restore target. RAMCode never stops

Failed to erase sectors.

Unspecified error -1

J-Link>

Hi @DaveNXP ,

It seems that you can connect to the core, but not erase nor flash it.

Could you try to restart the J-Link commander and halt the core with the 'h' command?

Kind regards,

Cis van Mierlo

Thanks for the answer cisvmierlo,

The thing is that at first I could correctly connect to the the core on the RDDRONE-BMS772 board, but after this first flash I cannot connect to core on the board anymore. So, I cannot send this 'h' command you recommend.

Do you have any other ideas?

Hi @DaveNXP,

Could you check if the voltage is OK according to the debugger?

Maybe the SW put the system in deep sleep and a button press is needed to start it up again.

Kind regards,

Cis van Mierlo

Hi Cis van Mierlo

The debugger provides 3,3V. And the output of the power supply connected to the RDDRONE board input is 22,2V. I do not understand very well what the problem may be and what changes and tests I should do.

I don't know any button to press or way to start it up again. I would really appreciate any help for this.

Thank you. Kind regards.

When you use JLINK software and a debugger to connect to the BMS, one of the first things JLINK.exe prints out is the voltage on the MCU/debug port.

It's possible that even with external power 22v or whatever, coming in to the BMS board, that the actual power supply feeding the MCU is not turned on.

There is a tiny physical button on the BMS which may wake up the MCU power supply.

https://nxp.gitbook.io/rddrone-bms772/user-guide/getting-to-know-the-hardware/board-organization

Hi, thank you for your answer.

I tried pushing the SW1 button. I tried with the reset jumper and without it.

I tried generating a reset pulse with a signal generator following the electrical specifications in the s32k1xx datasheet. https://www.nxp.com/docs/en/data-sheet/S32K-DS.pdf

I checked all the voltages.

If I connect the FTDI cable some garbage slash noise appears in the Tera Term console when I turn on and off the switch power supply.

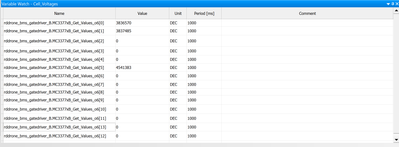

Hello, I was experimenting with the BMS772 this evening and was trying to display cell voltages. I have a 3s setup and for some reason one cell is consistently reading higher than the others. I confirmed via a multimeter that the cells are all roughly the same value. I tried this with two different battery packs as well. See my attached screenshot for more information. Notice, the BMS is consistently reading ~0.7 greater than the others. I am using Model-Based Development with a J-Link Debugger in FreeMaster. Any advice would be appreciated!

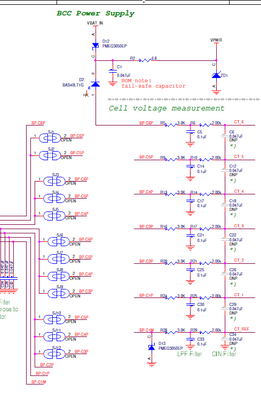

Hi @dmorvay,

I do not have experience with the Model-Based Development toolbox yet, so in this regard I can not check it.

For the HW:

Could you confirm that the soldered jumpers are SJ6, SJ10, SJ11 and SJ12 for 3S?

And the cell voltage filters are correctly in place:

Kind regards,

Cis van Mierlo

@cisvmierlo That seemed to do the trick! It appears that I failed to read that portion of the documentation about soldering those jumpers.

Another question regarding the OLED screen, I tried building and flashing the LED example onto the board, but the screen would not turn on. Is there anything special I need to do there? I was reading 3.3V on J23 between VCC and GND, but when I plugged the screen in, it would not turn on. Any suggestions? I didn't get a chance to check the D34 and D35 diodes today, but do those need to be moved if I am reading 3.3V?

Hi @dmorvay,

Great that soldering the correct jumpers solves the cell voltage issue!

For the OLED display, as I said I'm not familiar with the Model Based Design Toolbox examples.

Maybe they mean the RGB-LED which is on the board with the LED example?

The display delivered with the kit should support 3.3V.

But if you are interested in an BMS example project written in C with the NuttX RTOS (this includes the display to showcase battery values), see the example here: https://github.com/NXPHoverGames/RDDRONE-BMS772

PS: This is a graphical display, not a textual display. So each character needs to be drawn according to a specific font that is used.

Kind regards,

Cis van Mierlo

Hi @cisvmierlo, I appreciate the information! I will try again on the display. For reference, what is the I2C transmission voltage on the BMS772? Is it 5V or 3.3V I2C? I don't want to hook up a 5V I2C (say Arduino) and then damage the board if it is 3.3V.

Hi @dmorvay ,

The I2C voltage level is 3.3V.

This is the MCU voltage domain as well.

But there is 5V on the board which can be used to supply a display with 5V.

The schematic of the RDDRONE-BMS772 can be downloaded from the NXP webpage (click on design files or scroll down to the design resources):

https://www.nxp.com/design/designs/smart-battery-management-for-mobile-robotics:RDDRONE-BMS772

Kind regards,

Cis van Mierlo

Hi @cisvmierlo

Another question regarding I2C communication: when configuring the BMS772 as a slave, should the pins for SDA/SCL be PTB6 and PTB7 respectively or PTA2 and PTA3 respectively? Looking at the schematics, it seems like it is actually neither of these two options, but instead PTA0 and PTA1. Hence, I am slightly confused on how to setup the board as a slave for I2C communication.

Hi @dmorvay ,

The connector J18 can be used for SMBUS / I2CS.

The SMBUS_SCL and SMBUS_SDA lines are connected to this connector.

These lines are connector to PTA0 and PTA1, which support the LPI2C0_SCLS and /LPI2C0_SDAS peripheral.

Kind regards,

Cis van Mierlo

Hi @cisvmierlo

Two more questions based on your answer...

1. Can PTA2 and PTA3 (connector J23) be configured as an I2C slave? On the software side, it seems to be possible, but want to make sure everything checks out in both hardware and software.

2. How do you configure LPI2C0_SCLS and LPI2C0_SDAS? Do you have any references on how to configure this in C code and/or through Model Based Development? I am currently using Model Based Development, but I do not see any peripherals with LPI2C0_SCLS and LPI2C0_SDAS. Additionally, the I2C configuration block only has the options for PTA2/PTA3 or PTB6/PTB7. I am not exactly sure how to activate this output.

Hello @dmorvay,

Regarding the second question, the MBD Toolbox for S32K14x is built on top of the SDK for S32k14x. Unfortunately, it seems that the 4-wire mode is not supported for LPI2C by the SDK, therefore MBD toolbox doesn't support it either.

Best regards,

Bancila Sorin

Hi @dmorvay,

I'm not familiar with the MBDT example and what is supported in that toolbox.

For a C / C++ example I would advise you to take a look into the NuttX RTOS SW example.

In this example you can get the BMS data via I2C by reading the correct I2C addresses as stated in Table 6. SMBus variable list (Of chapter 7.5 How to use SMBus).

This example is located here: https://github.com/NXPHoverGames/RDDRONE-BMS772

It will need the NuttX RTOS sources as well: https://github.com/apache/nuttx

See the RDDRONE-BMS772 board in the NuttX repository:

https://github.com/apache/nuttx/tree/master/boards/arm/s32k1xx/rddrone-bms772

And the S32K1xx architecture specific logic:

https://github.com/apache/nuttx/tree/master/arch/arm/src/s32k1xx

I hope this helps you!

Kind regards,

Cis van Mierlo