- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

ls1012a GPIOs control by U-boot

Hi ,

I'm try to control GPIOs from U-boot.

I found gpio control code from ../ls1012afrdm/eth.c function name reset_phy() that used for reset PHY.

Then , I try to add more MASK bit to control GPIO1[16 :19] and enable GPIO1 on RCW.

Changing

#define MASK_ETH_PHY_RST 0x00000100 --> 0x000F0100

And I added debug print to read value that was set at DATA register looking it's doesn't change.

Clock Configuration:

CPU0(A53):800 MHz

Bus: 250 MHz DDR: 1000 MT/s

Reset Configuration Word (RCW):

00000000: 08000008 00000000 00000000 00000000

00000010: 35080000 c000000c 40000000 00001800

00000020: 00000000 00000000 00000000 00014171

00000030: 00000000 18c28120 00000096 00000000

I2C: ready

DRAM: 1022 MiB

SEC: RNG instantiated

Using SERDES1 Protocol: 13576 (0x3508)

MMC: FSL_SDHC: 0, FSL_SDHC: 1

SF: Detected S25FS512S_256K with page size 512 Bytes, erase size 128 KiB, total 64 MiB

PCIe1: Root Complex no link, regs @ 0x3400000

In: serial

Out: serial

Err: serial

Model: LS1012A RDB Board

Board: LS1012ARDB Version: RevB, boot from QSPI: bank1

SATA link 0 timeout.

AHCI 0001.0301 32 slots 1 ports 6 Gbps 0x1 impl SATA mode

flags: 64bit ncq pm clo only pmp fbss pio slum part ccc apst

Found 0 device(s).

SCSI: Net:

############# RESET PHY ###########

gpdat = 0001f000

###################################

Thank you,

Nattapong

Original Attachment has been moved to: eth.c.zip

Chapter 19 of the reference manual for the LS1012A gives a list of all of the GPIO pins that are output only, input only, or reserved. The pins that that did not read back the correct value happened because the pin is an output only port. This implies that read modify write will not work with the output only pins.

Was this ever resolved? I am having the same issue.

Hi , Justin

Seem like register not changed when read back , but it is working.

Look like it's not changing at 0x2300008

=> md 2300000

02300000: 00010f00 00000000 00000100 00000100 ................

02300010: 00000000 00000000 00000000 00000000 ................

02300020: 00000000 00000000 00000000 00000000 ................

02300030: 00000000 00000000 00000000 00000000 ................

02300040: 00000000 00000000 00000000 00000000 ................

02300050: 00000000 00000000 00000000 00000000 ................

02300060: 00000000 00000000 00000000 00000000 ................

02300070: 00000000 00000000 00000000 00000000 ................

02300080: 00000000 00000000 00000000 00000000 ................

02300090: 00000000 00000000 00000000 00000000 ................

023000a0: 00000000 00000000 00000000 00000000 ................

023000b0: 00000000 00000000 00000000 00000000 ................

023000c0: 00000000 00000000 00000000 00000000 ................

023000d0: 00000000 00000000 00000000 00000000 ................

023000e0: 00000000 00000000 00000000 00000000 ................

023000f0: 00000000 00000000 00000000 00000000 ................

=> mw 2300000 ffffffff

=> md 2300000

02300000: ffffffff 00000000 00000100 00000100 ................

02300010: 00000000 00000000 00000000 00000000 ................

02300020: 00000000 00000000 00000000 00000000 ................

02300030: 00000000 00000000 00000000 00000000 ................

02300040: 00000000 00000000 00000000 00000000 ................

02300050: 00000000 00000000 00000000 00000000 ................

02300060: 00000000 00000000 00000000 00000000 ................

02300070: 00000000 00000000 00000000 00000000 ................

02300080: 00000000 00000000 00000000 00000000 ................

02300090: 00000000 00000000 00000000 00000000 ................

023000a0: 00000000 00000000 00000000 00000000 ................

023000b0: 00000000 00000000 00000000 00000000 ................

023000c0: 00000000 00000000 00000000 00000000 ................

023000d0: 00000000 00000000 00000000 00000000 ................

023000e0: 00000000 00000000 00000000 00000000 ................

023000f0: 00000000 00000000 00000000 00000000 ................

=> mw 2300008 ffffffff

=> md 2300000

02300000: ffffffff 00000000 00f00100 00f00100 ................

02300010: 00000000 00000000 00000000 00000000 ................

02300020: 00000000 00000000 00000000 00000000 ................

02300030: 00000000 00000000 00000000 00000000 ................

02300040: 00000000 00000000 00000000 00000000 ................

02300050: 00000000 00000000 00000000 00000000 ................

02300060: 00000000 00000000 00000000 00000000 ................

02300070: 00000000 00000000 00000000 00000000 ................

02300080: 00000000 00000000 00000000 00000000 ................

02300090: 00000000 00000000 00000000 00000000 ................

023000a0: 00000000 00000000 00000000 00000000 ................

023000b0: 00000000 00000000 00000000 00000000 ................

023000c0: 00000000 00000000 00000000 00000000 ................

023000d0: 00000000 00000000 00000000 00000000 ................

023000e0: 00000000 00000000 00000000 00000000 ................

023000f0: 00000000 00000000 00000000 00000000 ................

=> mw 2300008 00000000

=> md 2300000

02300000: ffffffff 00000000 00000000 00f00100 ................

02300010: 00000000 00000000 00000000 00000000 ................

02300020: 00000000 00000000 00000000 00000000 ................

02300030: 00000000 00000000 00000000 00000000 ................

02300040: 00000000 00000000 00000000 00000000 ................

02300050: 00000000 00000000 00000000 00000000 ................

02300060: 00000000 00000000 00000000 00000000 ................

02300070: 00000000 00000000 00000000 00000000 ................

02300080: 00000000 00000000 00000000 00000000 ................

02300090: 00000000 00000000 00000000 00000000 ................

023000a0: 00000000 00000000 00000000 00000000 ................

023000b0: 00000000 00000000 00000000 00000000 ................

023000c0: 00000000 00000000 00000000 00000000 ................

023000d0: 00000000 00000000 00000000 00000000 ................

023000e0: 00000000 00000000 00000000 00000000 ................

023000f0: 00000000 00000000 00000000 00000000 ................

=>

In the provided log:

> => mw 2300008 ffffffff

> => md 2300000

> 02300000: ffffffff 00000000 00f00100 00f00100 ................

> => mw 2300008 00000000

> => md 2300000

> 02300000: ffffffff 00000000 00000000 00f00100 ................

> Look like it's not changing at 0x2300008

Not clear what do you mean.

Hi ufedor,

> => mw 2300008 ffffffff

> => md 2300000

> 02300000: ffffffff 00000000 00f00100 00f00100 ................

0x00f00100 should be 0xffffffff. Why it was changed only byte number 7 and first bit at byte number 2.

Thank you,

Nattapong

Yes, I also set all pin to output. by

=> mw 2300000 ffffffff

Yes, You are right.

But , I changed SDHC1_BASE to GPIOs

Hello ufedor,

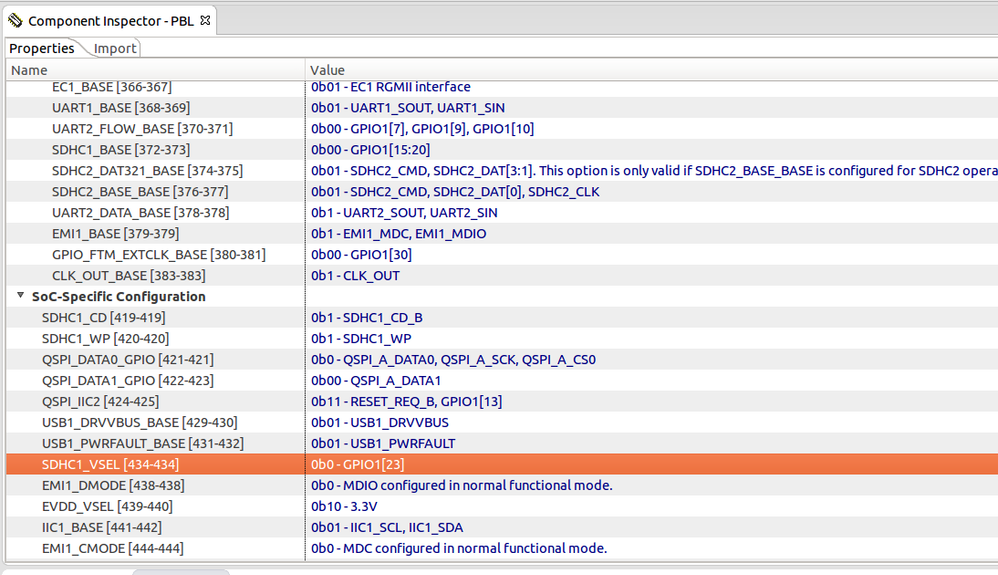

I'm using QCVS import PBL_0x35_0x08_800_250_1000_default.bin from LS1012A-SDK-AARCH64-IMAGE-20160830-yocto/ls1012ardb/

And change SDHC1_VSEL is GPIO and SDHC1_BASE are GPIOs.

Thank you,

Nattapong

Yes,

As I already attached eth.c

#define MASK_ETH_PHY_RST 0x000F0100

unsigned int val;

ccsr_gpio_t *pgpio = (void *)(CONFIG_SYS_GPIO1_ADDR);

setbits_be32(&pgpio->gpdir, MASK_ETH_PHY_RST);

.......

Thank you,

Nattapong