- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- PCIe Enumeration Question

PCIe Enumeration Question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PCIe Enumeration Question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

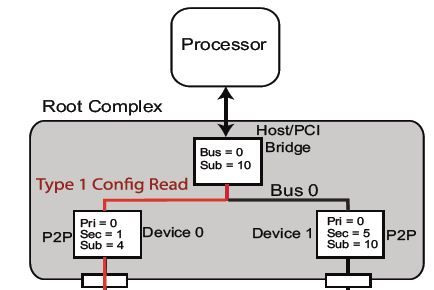

I have a question about enumeration and the distinction between the Host/PCI bridge and a P2P bridge in the Root Complex. I'm currently using a P1022DS as a bare board, no OS system for development while waiting on our real hardware. Since we have no OS I am working my way through the enumeration process. I have a simple C program based on the "Hello World" project the wizard creates for a bare board system and am using the debugger to step through and see what is going on by monitoring the config_data register. The .tcl script used by the debugger sets up the PCI1 controller at 0xE000A000. I can actually see the vendor ID information from the root complex down to an ethernet card I installed for testing purposes. Refer to the figure below.

I understand that in the enumeration process you poll Bus 0, Device 0, Function 0 and verify a valid Vendor ID and in my case that the device is a bridge. I'm presuming this is returning the device ID for the P2P bridge shown as device 0 in the figure. You then update the Primary bus = 0, Secondary bus = 1, and the Subordinate bus = 1 in the configuration space for BDF 0,0,0. (I realize the subordinate bus can be updated at the end which is why the figure shows the subordinate bus as = 4.) In some explanations of the process that I've read, it says that you also need to update the subordinate bus number on the Host/PCI bridge (shown as = 10 in the figure). How does one do this? It seems to me that using the configuration address/data registers will just update the P2P bridge and not the Host/PCI bridge. Any explanation would be greatly appreciated.

Thanks in advance.

Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe I found the answer. The P1022DS root complex contains the bridge to any downstream devices so there is no distinction. Once the BAR0 and memory base/limit registers are defined, you're done. Apparently this is one of the many things that is not defined in the PCIe specification and is system dependent.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I moved this thread from "Other Freescale Solutions" to "QorIQ Processors"...

Lukas