- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello everyone,

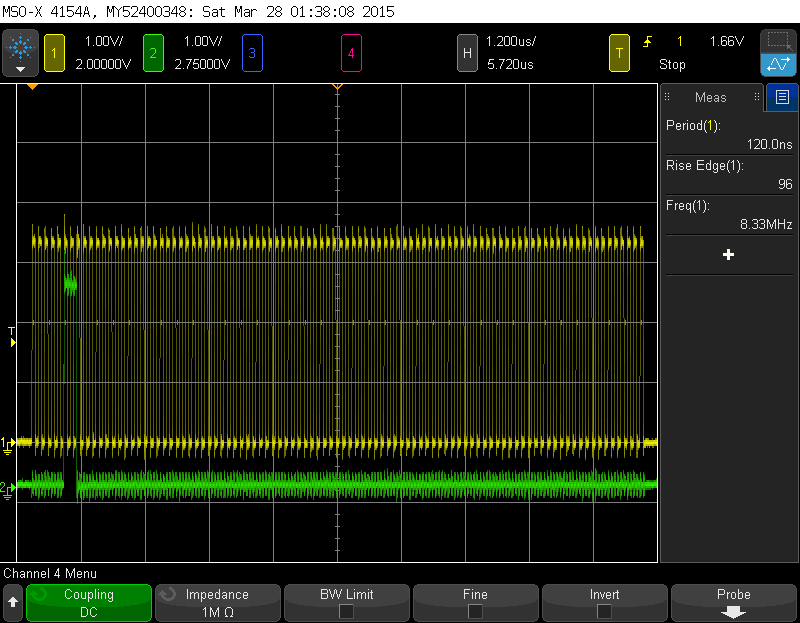

We're trying to boot from QSPI on the LS1021a twr board and we seem to be running into some problems. According to the LS1021 documentation, when the board is configured to boot from QSPI and comes out of reset, a READ command (0x03) is issued over the QSPI bus in an effort to begin reading in configuration information about the attached flash. We've managed to hook up an oscilloscope and monitor the pins between the LS1021 and the QSPI flash and we see an attempt at sending the READ command (we assume), but it appears that we do not read an 0x03 on the bus (we have attached screen captures of the clock and DQ0 lines). We witness multiple instances of the 0x03 command on the bus with no data being returned. This leads us to believe that the LS1021a is stuck continuously issuing it's QSPI boot process.

Below is the full interaction we see between the LS1021a and the QSPI flash 300us after power on reset deassertion.

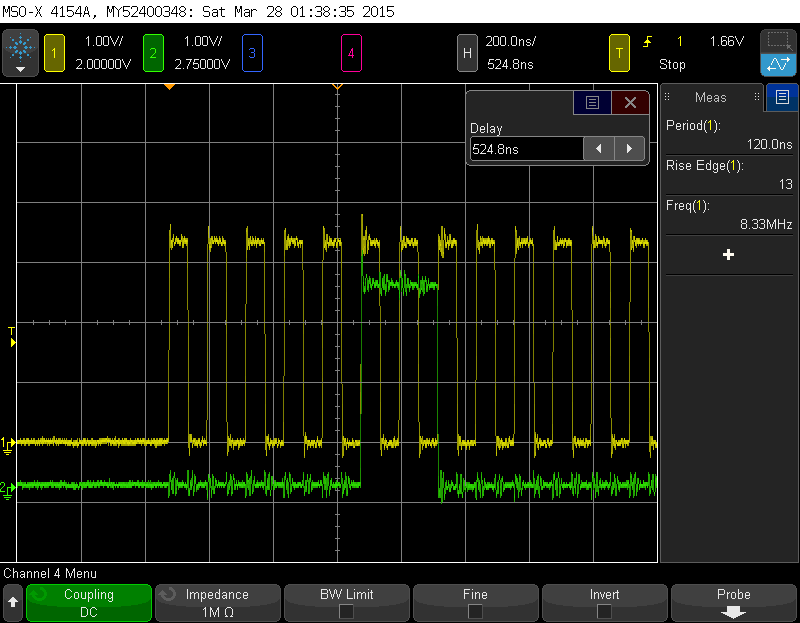

Below is zoomed in on the very beginning of the interaction between the LS1021a and the QSPI, where we believe the 0x03 is to be sent. But the timing of the signals below leads us to believe that a value of 0x03 is not being clocked in to the QSPI.

Are we correct in assuming that the QSPI flash must first be in its default single bit SPI (non-Quad mode) and also in XIP mode? It is our understanding that the QSPI controller eventually sets the flash into these modes, and that they need not be enable on power up. Is that line of thinking correct?

已解决! 转到解答。

Hi Patrick,

please check latest errata (LS1021A, LS1020A, and LS1022A Chip Errata, Rev F, 02/2015). Under A-007979, you can find: QSPI boot is not supported on the Rev 1.0 device (To be fixed in Rev 2.0).

If you can not wait for rev. 2. You can do the same as we did for our internal use. Add capacitor to D0 line to delay the signal. Solution is not tested in all conditions, but it works on the desk.

Br, Klemen

Hi Patrick,

please check latest errata (LS1021A, LS1020A, and LS1022A Chip Errata, Rev F, 02/2015). Under A-007979, you can find: QSPI boot is not supported on the Rev 1.0 device (To be fixed in Rev 2.0).

If you can not wait for rev. 2. You can do the same as we did for our internal use. Add capacitor to D0 line to delay the signal. Solution is not tested in all conditions, but it works on the desk.

Br, Klemen