- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: How to change LANEC to SATA1

How to change LANEC to SATA1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a customised board based on NXP LS1021A CPU, we made few changes for the SerDes LANEA to LANED, in details

LANEA/LANEB -> PCIEX2

LANC -> SATA1

LAND -> SGMII

I just changed the SRDS_PRTCL_S1=32 to 64 follow the datasheet "Table 32-2. Supported SerDes options" listed in rcw_1000_sdboot.rcw file, then recompiled RCW got binary and converted it to uboot format and was put it to ls102xa_rcw_sd.cfg file, then compiled uboot, now I used new uboot I can got LANEA/B and LAND working, just the SATA1 in LANC not working.

my question is: do I need change other parameters in rcw_1000_sdboot.rcw?

here is my rcw_1000_sdboot.rcw contents

--------

#include <../ls1021aqds/ls1021a.rcwi>

SYS_PLL_RAT=3

MEM_PLL_RAT=8

CGA_PLL1_RAT=10

SRDS_PRTCL_S1=64

SRDS_PLL_PD_S1=1

SRDS_DIV_PEX=1

USB3_REFCLK_SEL=0

USB3_CLK_FSEL=57

A7_ACE_CLKDIV=2

A7_DBG_CLKDIV=2

HWA_CGA_M1_CLK_SEL=1

PBI_SRC=6

DP_DIV=1

OCN_DIV=1

IFC_MODE=64

DRAM_LAT=1

SYS_PLL_SPD=1

UART_BASE=7

IFC_GRP_E1_EXT=4

EC1=4

EC2=2

QE-TDMA=6

QE-TDMB=6

SDHC=3

DVDD_VSEL=2

LVDD_VSEL=1

EVDD_VSEL=2

BVDD_VSEL=2

#include <../ls1021aqds/scfg_bit_reverse.rcw>

#include <../ls1021aqds/uboot_address.rcw>

----------

and uboot shows rcw binary hex format

----------

Reset Configuration Word (RCW):

00000000: 0608000a 00000000 00000000 00000000

00000010: 40000000 00407900 60040a00 21046000

00000020: 00000000 00000000 00000000 00038000

00000030: 00080000 881b7340 00000000 00000000

------------

Thank you!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

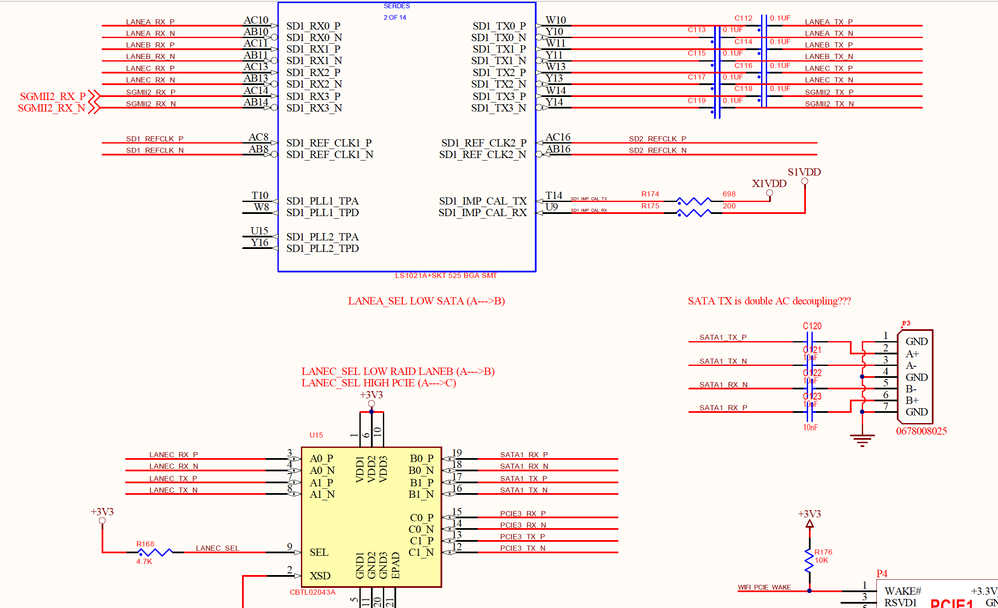

Provided schematics shows multiplexor.

Example driver:

MAX4951 SATA I/SATA II Bidirectional Re-Driver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please note that for the selected SerDes protocol 0x40 both PLLs have to be enabled - PLL2 is used by SATA (refer to the QorIQ LS1021A Reference Manual, Table 32-2. Supported SerDes options).

Modification:

SRDS_PLL_PD_S1=0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ufedor,

Thanks for your response.

I tried to change it and still can't get SATA link working, i used IOT SDK 0.4, is that version fixed SATA issue as i remember old version of SDK had a SATA issue.

------------

Reset Configuration Word (RCW):

00000000: 0608000a 00000000 00000000 00000000

00000010: 40000000 00007900 60040a00 21046000

00000020: 00000000 00000000 00000000 00038000

00000030: 00080000 881b7340 00000000 00000000

Board: LS1021AIOT

CPLD: V2.5

I2C: ready

DRAM: 1 GiB

Using SERDES1 Protocol: 64 (0x40)

MMC: FSL_SDHC: 0

EEPROM: Read failed.

PCIe1: Root Complex no link, regs @ 0x3400000

PCIe2: disabled

In: serial

Out: serial

Err: serial

SATA link 0 timeout.

AHCI 0001.0300 1 slots 1 ports ? Gbps 0x1 impl SATA mode

flags: 64bit ncq pm clo only pmp fbss pio slum part ccc

scanning bus for devices...

Found 0 device(s).

-----------

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The log shows that SATA should be operational.

Which device you connected and how exactly?

Please provide the processor connection schematics for inspection after creating a Technical Case:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ufedor,

here is the schematic of our design, we connect that SATA connector P3 as a ESATA.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you simulated or measured signal loss for the SATA lane?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

not yet, planning to do that. as we used SATA for connecting to an ESATA device, is it fine for the schematic and theory?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to available reference designs multiplexors for high-speed lanes are not recommended.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You mean it is not recommended for connect the LANE of LS1021a to an eSATA driver?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Provided schematics shows multiplexor.

Example driver:

MAX4951 SATA I/SATA II Bidirectional Re-Driver