- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 软件论坛

- :

- Processor Expert软件

- :

- Re: Where is PE floating point support?

Where is PE floating point support?

Using KDE 2.0.0, but same problem was present in 1.1.1, and Codewarrior before that.

I don't see any support for floating point in PE. That is, the Init_SCB component only has registers up to SCB_CPACR at 0xE000ED88, and doesn't have any of the floating point control registers starting at 0xE000EF34. I grepped all the .h files for the string "FPCCR", which is the standard name for the register at that address, and came up empty. The CP10 and CP11 fields in SCB_CPACR are zero, and the tool tip says "Reason why settings is disabled: Initialization of the bit is not supported by this component or the bit is not related to the selected peripheral."

So how is one supposed to enable floating point, and twiddle the FP configuration registers? Is there no way, other than to hard code hex addresses and data in the program?

已解决! 转到解答。

Hello Paul,

I have reproduced the problem in a PEx project without SDK. There are missing FPU registers. You can use following definitions from Kinetis SDK as the workaround of this issue.

I have reported this defect to the Processor Expert development team. They will fix this bug in a next release.

/** \ingroup CMSIS_core_register

\defgroup CMSIS_FPU Floating Point Unit (FPU)

\brief Type definitions for the Floating Point Unit (FPU)

@{

*/

/** \brief Structure type to access the Floating Point Unit (FPU).

*/

typedef struct

{

uint32_t RESERVED0[1];

volatile uint32_t FPCCR; /*!< Offset: 0x004 (R/W) Floating-Point Context Control Register */

volatile uint32_t FPCAR; /*!< Offset: 0x008 (R/W) Floating-Point Context Address Register */

volatile uint32_t FPDSCR; /*!< Offset: 0x00C (R/W) Floating-Point Default Status Control Register */

volatile uint32_t MVFR0; /*!< Offset: 0x010 (R/ ) Media and FP Feature Register 0 */

volatile uint32_t MVFR1; /*!< Offset: 0x014 (R/ ) Media and FP Feature Register 1 */

} FPU_Type;

/* Floating-Point Context Control Register */

#define FPU_FPCCR_ASPEN_Pos 31 /*!< FPCCR: ASPEN bit Position */

#define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) /*!< FPCCR: ASPEN bit Mask */

#define FPU_FPCCR_LSPEN_Pos 30 /*!< FPCCR: LSPEN Position */

#define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) /*!< FPCCR: LSPEN bit Mask */

#define FPU_FPCCR_MONRDY_Pos 8 /*!< FPCCR: MONRDY Position */

#define FPU_FPCCR_MONRDY_Msk (1UL << FPU_FPCCR_MONRDY_Pos) /*!< FPCCR: MONRDY bit Mask */

#define FPU_FPCCR_BFRDY_Pos 6 /*!< FPCCR: BFRDY Position */

#define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) /*!< FPCCR: BFRDY bit Mask */

#define FPU_FPCCR_MMRDY_Pos 5 /*!< FPCCR: MMRDY Position */

#define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) /*!< FPCCR: MMRDY bit Mask */

#define FPU_FPCCR_HFRDY_Pos 4 /*!< FPCCR: HFRDY Position */

#define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) /*!< FPCCR: HFRDY bit Mask */

#define FPU_FPCCR_THREAD_Pos 3 /*!< FPCCR: processor mode bit Position */

#define FPU_FPCCR_THREAD_Msk (1UL << FPU_FPCCR_THREAD_Pos) /*!< FPCCR: processor mode active bit Mask */

#define FPU_FPCCR_USER_Pos 1 /*!< FPCCR: privilege level bit Position */

#define FPU_FPCCR_USER_Msk (1UL << FPU_FPCCR_USER_Pos) /*!< FPCCR: privilege level bit Mask */

#define FPU_FPCCR_LSPACT_Pos 0 /*!< FPCCR: Lazy state preservation active bit Position */

#define FPU_FPCCR_LSPACT_Msk (1UL << FPU_FPCCR_LSPACT_Pos) /*!< FPCCR: Lazy state preservation active bit Mask */

/* Floating-Point Context Address Register */

#define FPU_FPCAR_ADDRESS_Pos 3 /*!< FPCAR: ADDRESS bit Position */

#define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) /*!< FPCAR: ADDRESS bit Mask */

/* Floating-Point Default Status Control Register */

#define FPU_FPDSCR_AHP_Pos 26 /*!< FPDSCR: AHP bit Position */

#define FPU_FPDSCR_AHP_Msk (1UL << FPU_FPDSCR_AHP_Pos) /*!< FPDSCR: AHP bit Mask */

#define FPU_FPDSCR_DN_Pos 25 /*!< FPDSCR: DN bit Position */

#define FPU_FPDSCR_DN_Msk (1UL << FPU_FPDSCR_DN_Pos) /*!< FPDSCR: DN bit Mask */

#define FPU_FPDSCR_FZ_Pos 24 /*!< FPDSCR: FZ bit Position */

#define FPU_FPDSCR_FZ_Msk (1UL << FPU_FPDSCR_FZ_Pos) /*!< FPDSCR: FZ bit Mask */

#define FPU_FPDSCR_RMode_Pos 22 /*!< FPDSCR: RMode bit Position */

#define FPU_FPDSCR_RMode_Msk (3UL << FPU_FPDSCR_RMode_Pos) /*!< FPDSCR: RMode bit Mask */

/* Media and FP Feature Register 0 */

#define FPU_MVFR0_FP_rounding_modes_Pos 28 /*!< MVFR0: FP rounding modes bits Position */

#define FPU_MVFR0_FP_rounding_modes_Msk (0xFUL << FPU_MVFR0_FP_rounding_modes_Pos) /*!< MVFR0: FP rounding modes bits Mask */

#define FPU_MVFR0_Short_vectors_Pos 24 /*!< MVFR0: Short vectors bits Position */

#define FPU_MVFR0_Short_vectors_Msk (0xFUL << FPU_MVFR0_Short_vectors_Pos) /*!< MVFR0: Short vectors bits Mask */

#define FPU_MVFR0_Square_root_Pos 20 /*!< MVFR0: Square root bits Position */

#define FPU_MVFR0_Square_root_Msk (0xFUL << FPU_MVFR0_Square_root_Pos) /*!< MVFR0: Square root bits Mask */

#define FPU_MVFR0_Divide_Pos 16 /*!< MVFR0: Divide bits Position */

#define FPU_MVFR0_Divide_Msk (0xFUL << FPU_MVFR0_Divide_Pos) /*!< MVFR0: Divide bits Mask */

#define FPU_MVFR0_FP_excep_trapping_Pos 12 /*!< MVFR0: FP exception trapping bits Position */

#define FPU_MVFR0_FP_excep_trapping_Msk (0xFUL << FPU_MVFR0_FP_excep_trapping_Pos) /*!< MVFR0: FP exception trapping bits Mask */

#define FPU_MVFR0_Double_precision_Pos 8 /*!< MVFR0: Double-precision bits Position */

#define FPU_MVFR0_Double_precision_Msk (0xFUL << FPU_MVFR0_Double_precision_Pos) /*!< MVFR0: Double-precision bits Mask */

#define FPU_MVFR0_Single_precision_Pos 4 /*!< MVFR0: Single-precision bits Position */

#define FPU_MVFR0_Single_precision_Msk (0xFUL << FPU_MVFR0_Single_precision_Pos) /*!< MVFR0: Single-precision bits Mask */

#define FPU_MVFR0_A_SIMD_registers_Pos 0 /*!< MVFR0: A_SIMD registers bits Position */

#define FPU_MVFR0_A_SIMD_registers_Msk (0xFUL << FPU_MVFR0_A_SIMD_registers_Pos) /*!< MVFR0: A_SIMD registers bits Mask */

/* Media and FP Feature Register 1 */

#define FPU_MVFR1_FP_fused_MAC_Pos 28 /*!< MVFR1: FP fused MAC bits Position */

#define FPU_MVFR1_FP_fused_MAC_Msk (0xFUL << FPU_MVFR1_FP_fused_MAC_Pos) /*!< MVFR1: FP fused MAC bits Mask */

#define FPU_MVFR1_FP_HPFP_Pos 24 /*!< MVFR1: FP HPFP bits Position */

#define FPU_MVFR1_FP_HPFP_Msk (0xFUL << FPU_MVFR1_FP_HPFP_Pos) /*!< MVFR1: FP HPFP bits Mask */

#define FPU_MVFR1_D_NaN_mode_Pos 4 /*!< MVFR1: D_NaN mode bits Position */

#define FPU_MVFR1_D_NaN_mode_Msk (0xFUL << FPU_MVFR1_D_NaN_mode_Pos) /*!< MVFR1: D_NaN mode bits Mask */

#define FPU_MVFR1_FtZ_mode_Pos 0 /*!< MVFR1: FtZ mode bits Position */

#define FPU_MVFR1_FtZ_mode_Msk (0xFUL << FPU_MVFR1_FtZ_mode_Pos) /*!< MVFR1: FtZ mode bits Mask */

/* Memory mapping of Cortex-M4 Hardware - FP extension */

#define SCS_BASE (0xE000E000UL) /*!< System Control Space Base Address */

#define FPU_BASE (SCS_BASE + 0x0F30UL) /*!< Floating Point Unit */

#define FPU_BASE_PTR ((FPU_Type*) FPU_BASE) /*!< Floating Point Unit */

#define FPU_FPCCR_REG(base) ((base)->FPCCR)

#define FPU_FPCAR_REG(base) ((base)->FPCAR)

#define FPU_FPDSCR_REG(base) ((base)->FPDSCR)

#define FPU_MVFR0_REG(base) ((base)->MVFR0)

#define FPU_MVFR1_REG(base) ((base)->MVFR1)

#define FPU_FPCCR FPU_FPCCR_REG(FPU_BASE_PTR)

#define FPU_FPCAR FPU_FPCAR_REG(FPU_BASE_PTR)

#define FPU_FPDSCR FPU_FPDSCR_REG(FPU_BASE_PTR)

#define FPU_MVFR0 FPU_MVFR0_REG(FPU_BASE_PTR)

#define FPU_MVFR1 FPU_MVFR1_REG(FPU_BASE_PTR)

Best Regards,

Marek Neuzil

I don't think there is a setting in the components itself.

But the startup code (startup.c) enables the FPU this way in KDS v2.0.0:

void __attribute__ ((weak)) __init_registers(void)

{

#if defined(SCB_CPACR)

/* Initialize FPU */

SCB_CPACR |= SCB_CPACR_CP10(3U) | SCB_CPACR_CP11(3U);

#endif

}

Okay, so the startup code enables the FPU, even though PE doesn't show this in the relevant fields of the SCB_CPACR register. That's nice. But there is still no mention of those higher-addressed SCB registers that configure the FPU. They exist. They're real registers in the core. They ought to be listed in the header files that contain the port addresses and bit masks. They also ought to be included in whatever XML files contain the list of parameters in the PE SCB component. How hard can that be for Freescale to fix? Or is there someplace else I should report this deficiency? Is there a bug tracker?

Hello Paul,

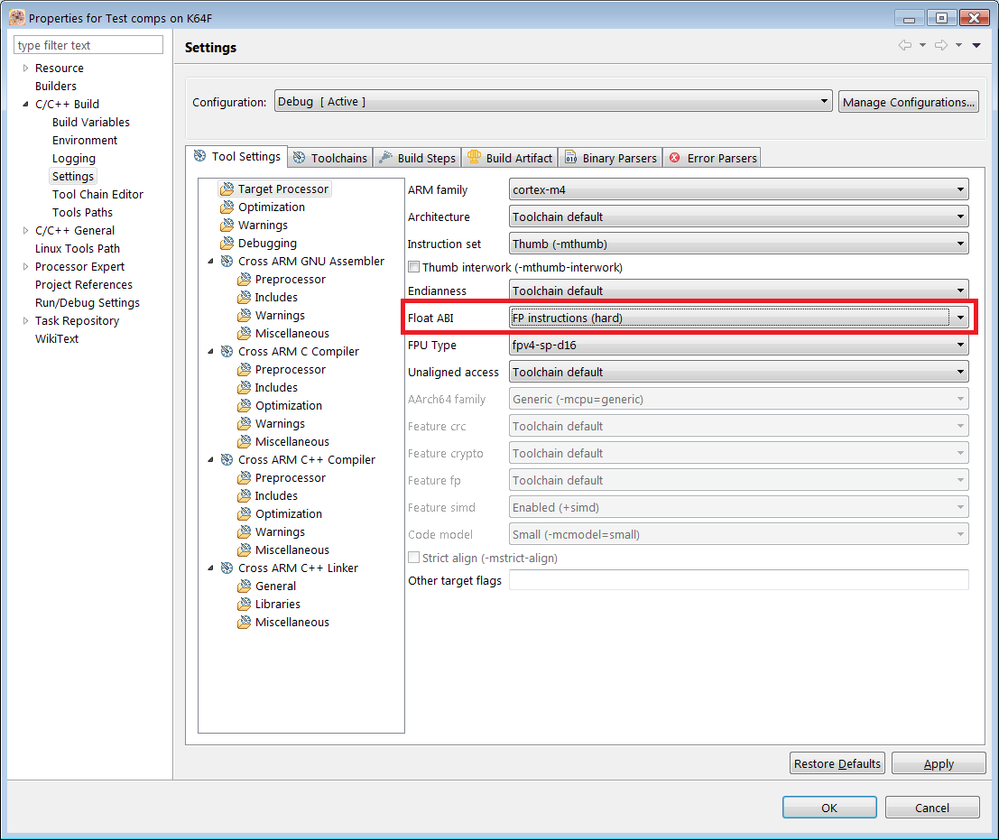

In the KDS 3.0.0 the floating point is configured on the Target Processor tab - Float ABI option of the project Properties (see the Properties, C/C++ Build/Settings, Target Processor – Float AB; see the following screenshot)

The FPU (SCB_CPARC – CP10 and CP11 bits) are set according to this FPU configuration of the Float ABI option of the project (this options is used for configuration of the compiler and linker):

This options specify the value of the -mfloat-abi compiler parameter. There are possible following values:

-mfloat-abi=name

Specifies which floating-point ABI to use. Permissible values are: ‘soft’, ‘softfp’ and ‘hard’.

Specifying ‘soft’ causes GCC to generate output containing library calls for floating-point operations. ‘softfp’ allows the generation of code using hardware floating-point instructions, but still uses the soft-float calling conventions. ‘hard’ allows generation of floating-point instructions and uses FPU-specific calling conventions.

The default depends on the specific target configuration. Note that the hard-float and soft-float ABIs are not link-compatible; you must compile your entire program with the same ABI, and link with a compatible set of libraries.

Based on this selection, there are configured CP10 and CP11 bits in the startup file:

core_cm4.h header CMSIS file contains folowing defintions:

#if defined (__VFP_FP__) && !defined(__SOFTFP__)

#if (__FPU_PRESENT == 1)

#define __FPU_USED 1

#else

#warning "Compiler generates FPU instructions for a device without an FPU (check __FPU_PRESENT)"

#define __FPU_USED 0

#endif

#else

#define __FPU_USED 0

#endif

The SystemInit() function in the system_<derivative name>.c contains following code:

#if ((__FPU_PRESENT == 1) && (__FPU_USED == 1))

SCB->CPACR |= ((3UL << 10*2) | (3UL << 11*2)); /* set CP10, CP11 Full Access */

#endif /* ((__FPU_PRESENT == 1) && (__FPU_USED == 1)) */

Please note, that definitions of CP10 and CP11 bits are available in the Static_Code/IO_Map/core_cm4_PEx.h (for example for MK64FN1M0 derivative). The FPPCR register definition is available in the SDK/platform/CMSIS/Include/core_cm4.h CMSIS header file.

Best Regards,

Marek Neuzil

Yes, I got that. That was already selected.

My main complaint is that while the Init_SCB component and the header files list all the registers listed in Table B3-4 in the ARMv7-M Architecture Reference Manual, it leaves out the floating point configuration registers listed in Table B3-5. This includes FPCCR, FPCAR, FPDSCR, MVFR0 and MVFR1. I need to clear the ASPEN and LSPEN bits in FPCCR, so that interrupts don't waste time or space stacking the floating point registers, because I know I'm never going to use floating point in an interrupt handler. Obviously, I've declared my own symbols and used them, but these are real registers that exist, and the fact that they're missing from the PE component and the headers is a bug. If this isn't the place to report that, where should I do that?

Hello Paul,

I have reproduced the problem in a PEx project without SDK. There are missing FPU registers. You can use following definitions from Kinetis SDK as the workaround of this issue.

I have reported this defect to the Processor Expert development team. They will fix this bug in a next release.

/** \ingroup CMSIS_core_register

\defgroup CMSIS_FPU Floating Point Unit (FPU)

\brief Type definitions for the Floating Point Unit (FPU)

@{

*/

/** \brief Structure type to access the Floating Point Unit (FPU).

*/

typedef struct

{

uint32_t RESERVED0[1];

volatile uint32_t FPCCR; /*!< Offset: 0x004 (R/W) Floating-Point Context Control Register */

volatile uint32_t FPCAR; /*!< Offset: 0x008 (R/W) Floating-Point Context Address Register */

volatile uint32_t FPDSCR; /*!< Offset: 0x00C (R/W) Floating-Point Default Status Control Register */

volatile uint32_t MVFR0; /*!< Offset: 0x010 (R/ ) Media and FP Feature Register 0 */

volatile uint32_t MVFR1; /*!< Offset: 0x014 (R/ ) Media and FP Feature Register 1 */

} FPU_Type;

/* Floating-Point Context Control Register */

#define FPU_FPCCR_ASPEN_Pos 31 /*!< FPCCR: ASPEN bit Position */

#define FPU_FPCCR_ASPEN_Msk (1UL << FPU_FPCCR_ASPEN_Pos) /*!< FPCCR: ASPEN bit Mask */

#define FPU_FPCCR_LSPEN_Pos 30 /*!< FPCCR: LSPEN Position */

#define FPU_FPCCR_LSPEN_Msk (1UL << FPU_FPCCR_LSPEN_Pos) /*!< FPCCR: LSPEN bit Mask */

#define FPU_FPCCR_MONRDY_Pos 8 /*!< FPCCR: MONRDY Position */

#define FPU_FPCCR_MONRDY_Msk (1UL << FPU_FPCCR_MONRDY_Pos) /*!< FPCCR: MONRDY bit Mask */

#define FPU_FPCCR_BFRDY_Pos 6 /*!< FPCCR: BFRDY Position */

#define FPU_FPCCR_BFRDY_Msk (1UL << FPU_FPCCR_BFRDY_Pos) /*!< FPCCR: BFRDY bit Mask */

#define FPU_FPCCR_MMRDY_Pos 5 /*!< FPCCR: MMRDY Position */

#define FPU_FPCCR_MMRDY_Msk (1UL << FPU_FPCCR_MMRDY_Pos) /*!< FPCCR: MMRDY bit Mask */

#define FPU_FPCCR_HFRDY_Pos 4 /*!< FPCCR: HFRDY Position */

#define FPU_FPCCR_HFRDY_Msk (1UL << FPU_FPCCR_HFRDY_Pos) /*!< FPCCR: HFRDY bit Mask */

#define FPU_FPCCR_THREAD_Pos 3 /*!< FPCCR: processor mode bit Position */

#define FPU_FPCCR_THREAD_Msk (1UL << FPU_FPCCR_THREAD_Pos) /*!< FPCCR: processor mode active bit Mask */

#define FPU_FPCCR_USER_Pos 1 /*!< FPCCR: privilege level bit Position */

#define FPU_FPCCR_USER_Msk (1UL << FPU_FPCCR_USER_Pos) /*!< FPCCR: privilege level bit Mask */

#define FPU_FPCCR_LSPACT_Pos 0 /*!< FPCCR: Lazy state preservation active bit Position */

#define FPU_FPCCR_LSPACT_Msk (1UL << FPU_FPCCR_LSPACT_Pos) /*!< FPCCR: Lazy state preservation active bit Mask */

/* Floating-Point Context Address Register */

#define FPU_FPCAR_ADDRESS_Pos 3 /*!< FPCAR: ADDRESS bit Position */

#define FPU_FPCAR_ADDRESS_Msk (0x1FFFFFFFUL << FPU_FPCAR_ADDRESS_Pos) /*!< FPCAR: ADDRESS bit Mask */

/* Floating-Point Default Status Control Register */

#define FPU_FPDSCR_AHP_Pos 26 /*!< FPDSCR: AHP bit Position */

#define FPU_FPDSCR_AHP_Msk (1UL << FPU_FPDSCR_AHP_Pos) /*!< FPDSCR: AHP bit Mask */

#define FPU_FPDSCR_DN_Pos 25 /*!< FPDSCR: DN bit Position */

#define FPU_FPDSCR_DN_Msk (1UL << FPU_FPDSCR_DN_Pos) /*!< FPDSCR: DN bit Mask */

#define FPU_FPDSCR_FZ_Pos 24 /*!< FPDSCR: FZ bit Position */

#define FPU_FPDSCR_FZ_Msk (1UL << FPU_FPDSCR_FZ_Pos) /*!< FPDSCR: FZ bit Mask */

#define FPU_FPDSCR_RMode_Pos 22 /*!< FPDSCR: RMode bit Position */

#define FPU_FPDSCR_RMode_Msk (3UL << FPU_FPDSCR_RMode_Pos) /*!< FPDSCR: RMode bit Mask */

/* Media and FP Feature Register 0 */

#define FPU_MVFR0_FP_rounding_modes_Pos 28 /*!< MVFR0: FP rounding modes bits Position */

#define FPU_MVFR0_FP_rounding_modes_Msk (0xFUL << FPU_MVFR0_FP_rounding_modes_Pos) /*!< MVFR0: FP rounding modes bits Mask */

#define FPU_MVFR0_Short_vectors_Pos 24 /*!< MVFR0: Short vectors bits Position */

#define FPU_MVFR0_Short_vectors_Msk (0xFUL << FPU_MVFR0_Short_vectors_Pos) /*!< MVFR0: Short vectors bits Mask */

#define FPU_MVFR0_Square_root_Pos 20 /*!< MVFR0: Square root bits Position */

#define FPU_MVFR0_Square_root_Msk (0xFUL << FPU_MVFR0_Square_root_Pos) /*!< MVFR0: Square root bits Mask */

#define FPU_MVFR0_Divide_Pos 16 /*!< MVFR0: Divide bits Position */

#define FPU_MVFR0_Divide_Msk (0xFUL << FPU_MVFR0_Divide_Pos) /*!< MVFR0: Divide bits Mask */

#define FPU_MVFR0_FP_excep_trapping_Pos 12 /*!< MVFR0: FP exception trapping bits Position */

#define FPU_MVFR0_FP_excep_trapping_Msk (0xFUL << FPU_MVFR0_FP_excep_trapping_Pos) /*!< MVFR0: FP exception trapping bits Mask */

#define FPU_MVFR0_Double_precision_Pos 8 /*!< MVFR0: Double-precision bits Position */

#define FPU_MVFR0_Double_precision_Msk (0xFUL << FPU_MVFR0_Double_precision_Pos) /*!< MVFR0: Double-precision bits Mask */

#define FPU_MVFR0_Single_precision_Pos 4 /*!< MVFR0: Single-precision bits Position */

#define FPU_MVFR0_Single_precision_Msk (0xFUL << FPU_MVFR0_Single_precision_Pos) /*!< MVFR0: Single-precision bits Mask */

#define FPU_MVFR0_A_SIMD_registers_Pos 0 /*!< MVFR0: A_SIMD registers bits Position */

#define FPU_MVFR0_A_SIMD_registers_Msk (0xFUL << FPU_MVFR0_A_SIMD_registers_Pos) /*!< MVFR0: A_SIMD registers bits Mask */

/* Media and FP Feature Register 1 */

#define FPU_MVFR1_FP_fused_MAC_Pos 28 /*!< MVFR1: FP fused MAC bits Position */

#define FPU_MVFR1_FP_fused_MAC_Msk (0xFUL << FPU_MVFR1_FP_fused_MAC_Pos) /*!< MVFR1: FP fused MAC bits Mask */

#define FPU_MVFR1_FP_HPFP_Pos 24 /*!< MVFR1: FP HPFP bits Position */

#define FPU_MVFR1_FP_HPFP_Msk (0xFUL << FPU_MVFR1_FP_HPFP_Pos) /*!< MVFR1: FP HPFP bits Mask */

#define FPU_MVFR1_D_NaN_mode_Pos 4 /*!< MVFR1: D_NaN mode bits Position */

#define FPU_MVFR1_D_NaN_mode_Msk (0xFUL << FPU_MVFR1_D_NaN_mode_Pos) /*!< MVFR1: D_NaN mode bits Mask */

#define FPU_MVFR1_FtZ_mode_Pos 0 /*!< MVFR1: FtZ mode bits Position */

#define FPU_MVFR1_FtZ_mode_Msk (0xFUL << FPU_MVFR1_FtZ_mode_Pos) /*!< MVFR1: FtZ mode bits Mask */

/* Memory mapping of Cortex-M4 Hardware - FP extension */

#define SCS_BASE (0xE000E000UL) /*!< System Control Space Base Address */

#define FPU_BASE (SCS_BASE + 0x0F30UL) /*!< Floating Point Unit */

#define FPU_BASE_PTR ((FPU_Type*) FPU_BASE) /*!< Floating Point Unit */

#define FPU_FPCCR_REG(base) ((base)->FPCCR)

#define FPU_FPCAR_REG(base) ((base)->FPCAR)

#define FPU_FPDSCR_REG(base) ((base)->FPDSCR)

#define FPU_MVFR0_REG(base) ((base)->MVFR0)

#define FPU_MVFR1_REG(base) ((base)->MVFR1)

#define FPU_FPCCR FPU_FPCCR_REG(FPU_BASE_PTR)

#define FPU_FPCAR FPU_FPCAR_REG(FPU_BASE_PTR)

#define FPU_FPDSCR FPU_FPDSCR_REG(FPU_BASE_PTR)

#define FPU_MVFR0 FPU_MVFR0_REG(FPU_BASE_PTR)

#define FPU_MVFR1 FPU_MVFR1_REG(FPU_BASE_PTR)

Best Regards,

Marek Neuzil