- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- SDRAM: IS42S16100H-6TLI not working with IMXRT1064

SDRAM: IS42S16100H-6TLI not working with IMXRT1064

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

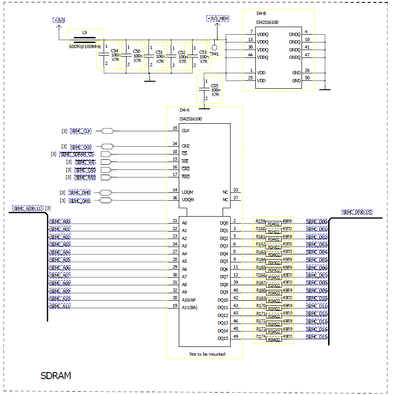

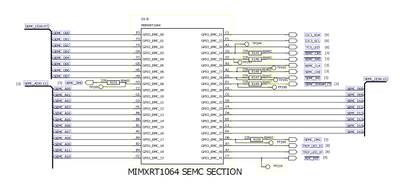

I need support for configuration the SEMC controller for the SDRAM access. Below is the controller and SDRAM we are using and you can find the schematic below.

Microcontroller : MIMXRT1064CVJ5B

SDRAM: IS42S16100H-6TLI from Integrated Silicon Solution, Inc. (ISSI)

================================================================

code :

semc_config_t config;

semc_sdram_config_t sdramconfig;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000;

sdramconfig.memsize_kbytes = 2 * 1024; /* 32MB = 32*1024*1KBytes*/

sdramconfig.portSize = kSEMC_PortSize8Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen4;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_8bit;

sdramconfig.casLatency = kSEMC_LatencyThree;

sdramconfig.tPrecharge2Act_Ns = 18; /* Trp 18ns */

sdramconfig.tAct2ReadWrite_Ns = 18; /* Trcd 18ns */

sdramconfig.tRefreshRecovery_Ns = 67; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 12; /* 12ns */

sdramconfig.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 42; /* Tras 42ns */

sdramconfig.tSelfRefRecovery_Ns = 67;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 60;

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq);

}

================================================================

Issue:

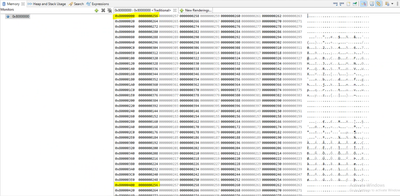

I am writing 1 to 200 from starting location 0x8000_0000 continuously.

when writing to the location 0x8000_0200 will also overwrite the the address 0x8000_0000.

similarly writing to address 0x8000_2001 will overwrite the the address 0x8000_0004 it will continue.

please let me the issue with my configuration or schematic.

I am using the SDK procided sdk project "evkmimxrt1064_semc"

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

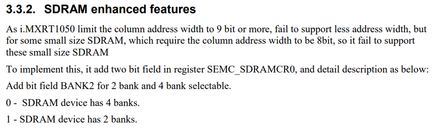

Another thing worth noting is the use of the bit field BANK2 from the SDRAM Control Register 0. This bit should be set when the SDRAM device has 2 banks, which in this case it does. It is not fully implemented on the SDK example by default, but adding the BANK2 macro on the SEMC configuration would do it (fsl_semc.c):

base->SDRAMCR0 = SEMC_SDRAMCR0_PS(config->portSize) | SEMC_SDRAMCR0_BL(config->burstLen) | SEMC_SDRAMCR0_COL(config->columnAddrBitNum) | SEMC_SDRAMCR0_CL(config->casLatency) | SEMC_SDRAMCR0_BANK2_MASK;

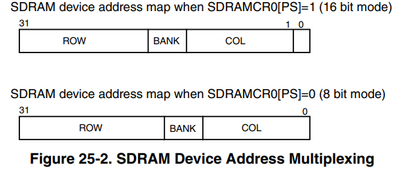

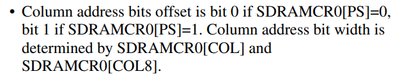

This is image is from Application Note: AN12240

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another thing worth noting is the use of the bit field BANK2 from the SDRAM Control Register 0. This bit should be set when the SDRAM device has 2 banks, which in this case it does. It is not fully implemented on the SDK example by default, but adding the BANK2 macro on the SEMC configuration would do it (fsl_semc.c):

base->SDRAMCR0 = SEMC_SDRAMCR0_PS(config->portSize) | SEMC_SDRAMCR0_BL(config->burstLen) | SEMC_SDRAMCR0_COL(config->columnAddrBitNum) | SEMC_SDRAMCR0_CL(config->casLatency) | SEMC_SDRAMCR0_BANK2_MASK;

This is image is from Application Note: AN12240

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @rajendrac4u,

I believe the Bank Address Bits might be erroneous. The IS42S16100H’s Bank Address pin (A11) should be connected to SEMC_BA0 (GPIO_EMC_21) in order to properly differentiate between memory banks.

BR,

Edwin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @EdwinHz

Thanks for the reply.

I have done the changes suggested by you. Connected SEMC BA0 to SDRAM A11 pin.

now i am able to write from address 0x8000_0000 to 0x8000_0400.

after that it will overwrite from 0x8000_0000.

can you please help me.

Thanks

Rajendra

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the code snippet you attach, I see the port size was kept at 8 bits, considering that the IS42S16100 is a 16 bit SDRAM, I believe this should also be changed, since the whole address map changes according to the port size bit:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content