- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- Re: Incorrect behavior for FIRC Fast IRC Regulator settings in Processor Expert ?

Incorrect behavior for FIRC Fast IRC Regulator settings in Processor Expert ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

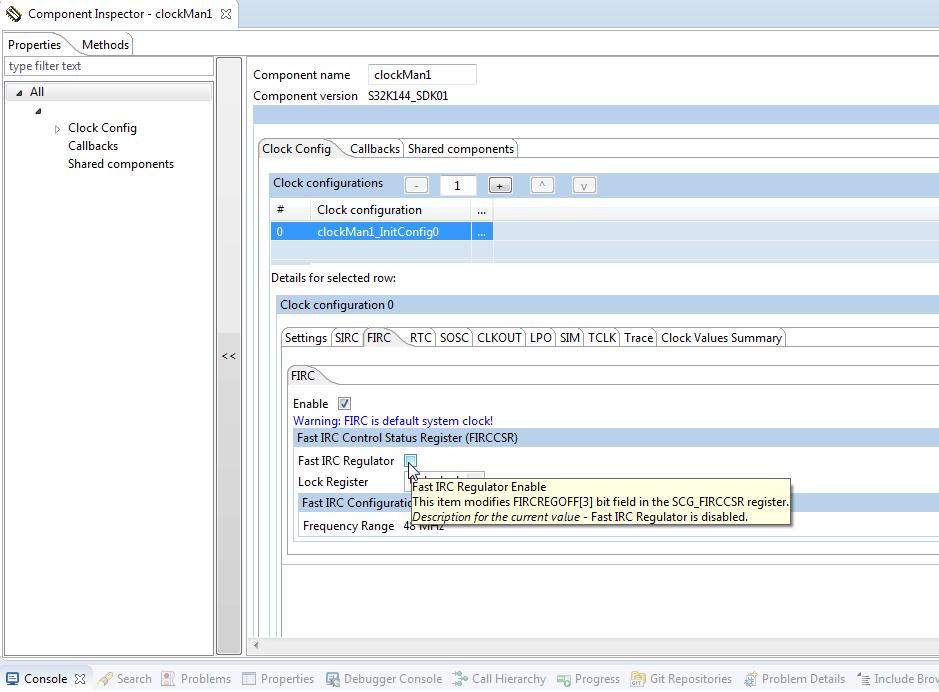

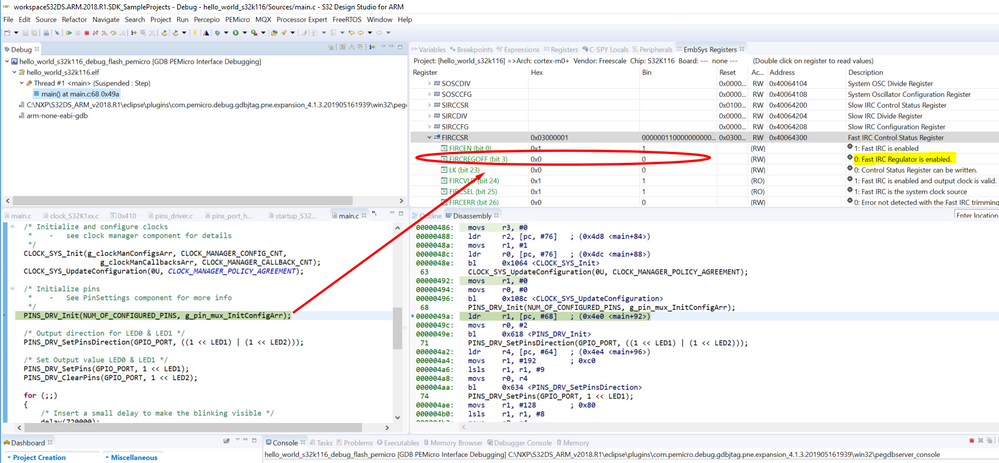

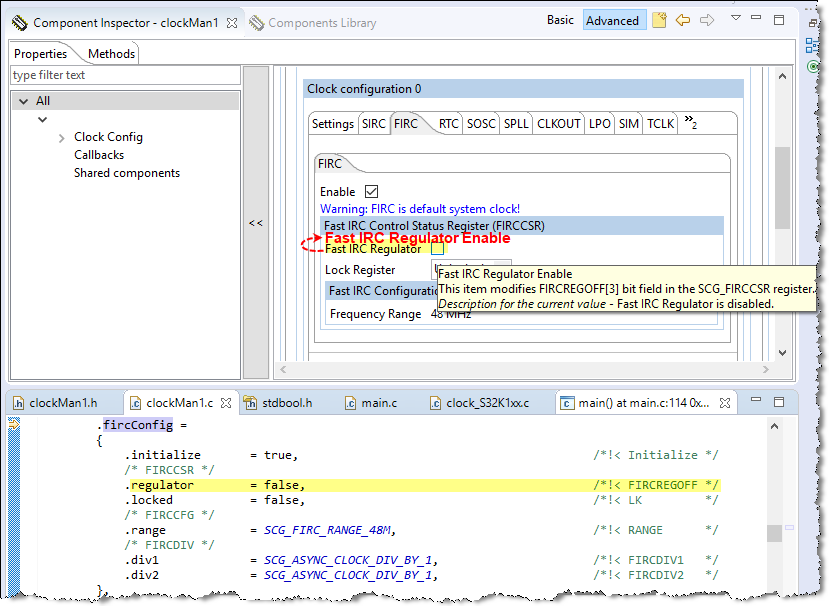

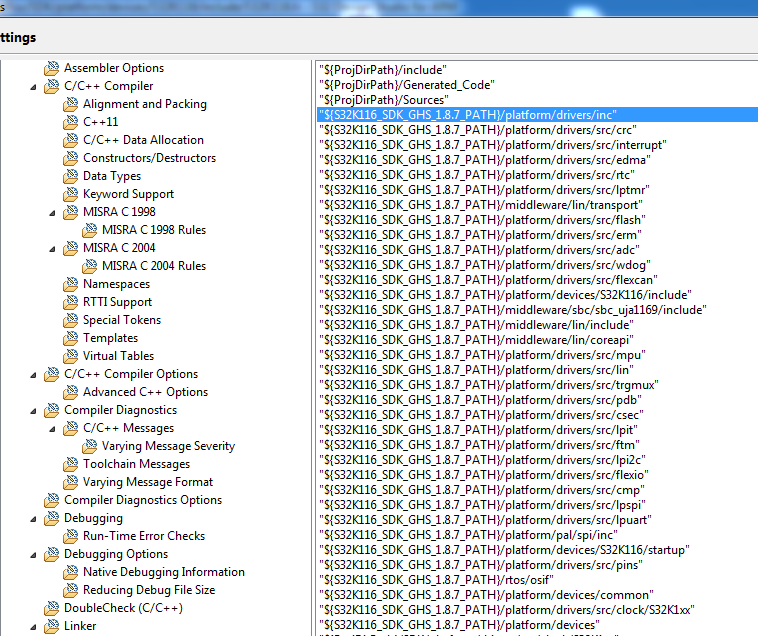

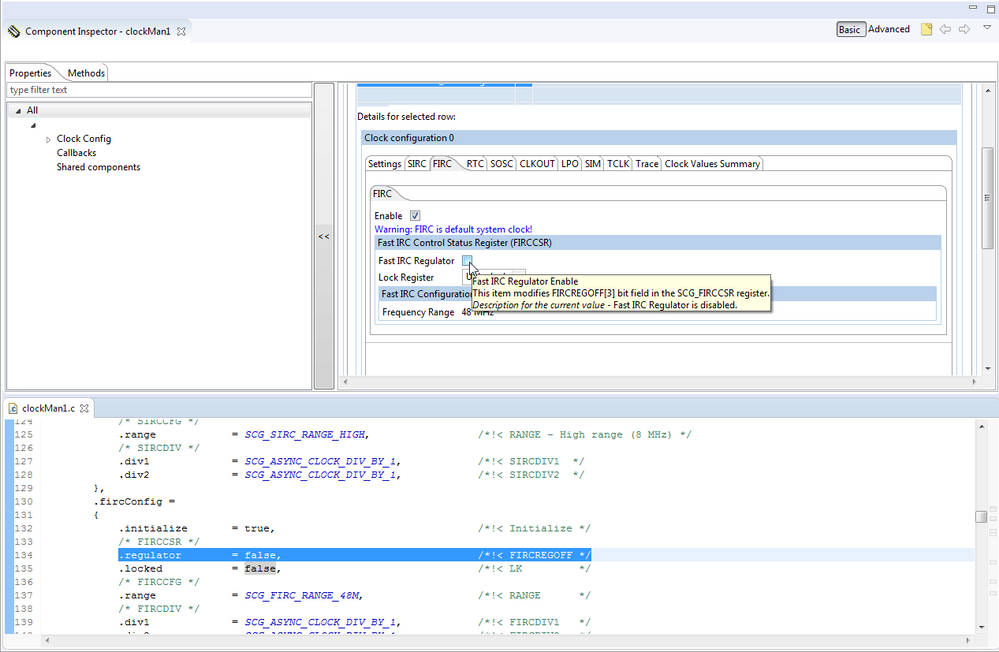

When "Fast IRC Regulator" check box is checked (in below figure the checkbox is not checked) bit "FIRCREGOFF" from register "FIRCCSR" in System Clock Generator (SCG) module is SET (=1). That means the regulator is OFF.

This seems to be in the opposition with the description of the tool-tip (below image).

To have the FIRCREGOFF bit to 0 (FIRC Regulator enabled) I have to un-check the box (like is below).

I use S32 Design Studio for ARM, Version 2018.R1, Build id: 180815

I hope this helps.

Best Regards,

Ciprian Salageanu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the feedback from internal team:

Could you please double check and told me which S32K SDK Version you are using?

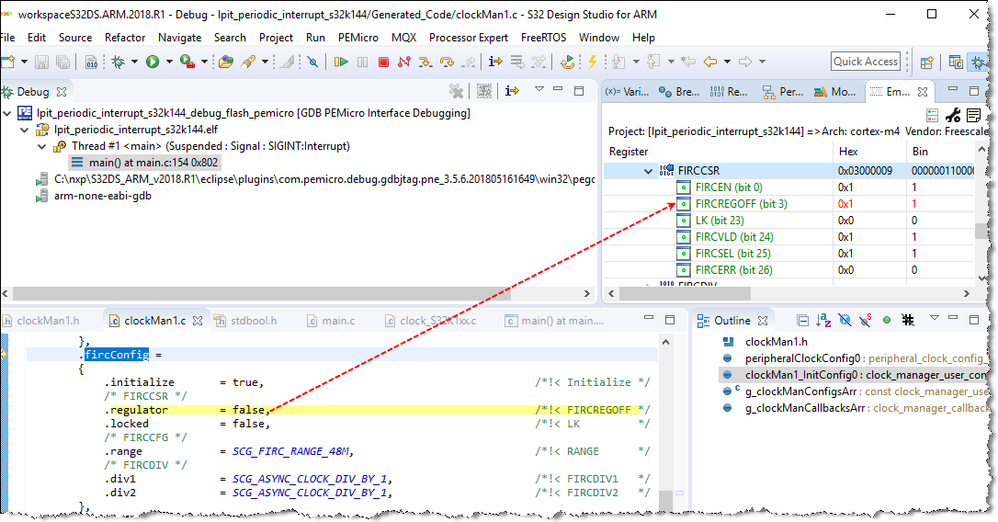

I checked both S32K14x RTM2.0.0(not support S32K11x) and S32K1xx RTM 3.0.0, they works as expected, no bugs:

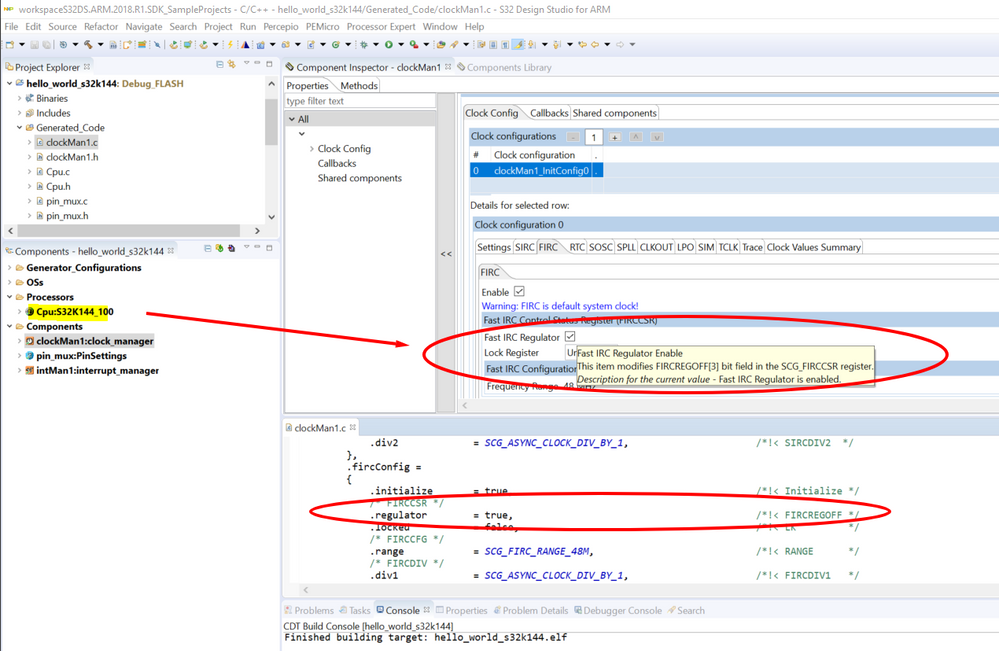

S32K144 FIRC configure tab in Processor Expert clock_manager component(both S32K1xx RTM 3.0.0 and S32K14x RTM2.0.0 are the same):

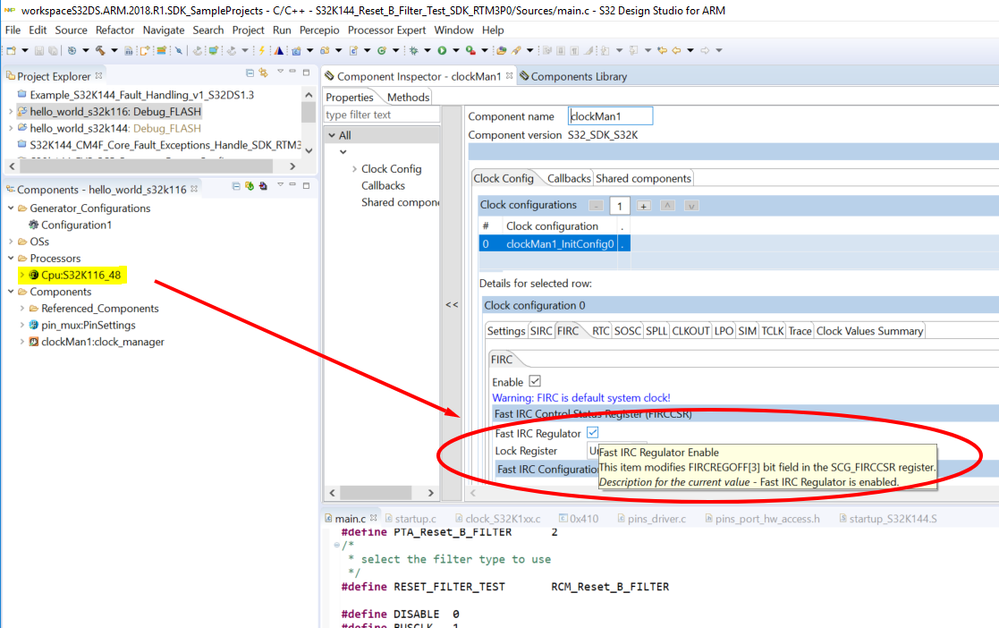

S32K116 FIRC configure tab in Processor Expert clock_manager component(S32K1xx RTM 3.0.0):

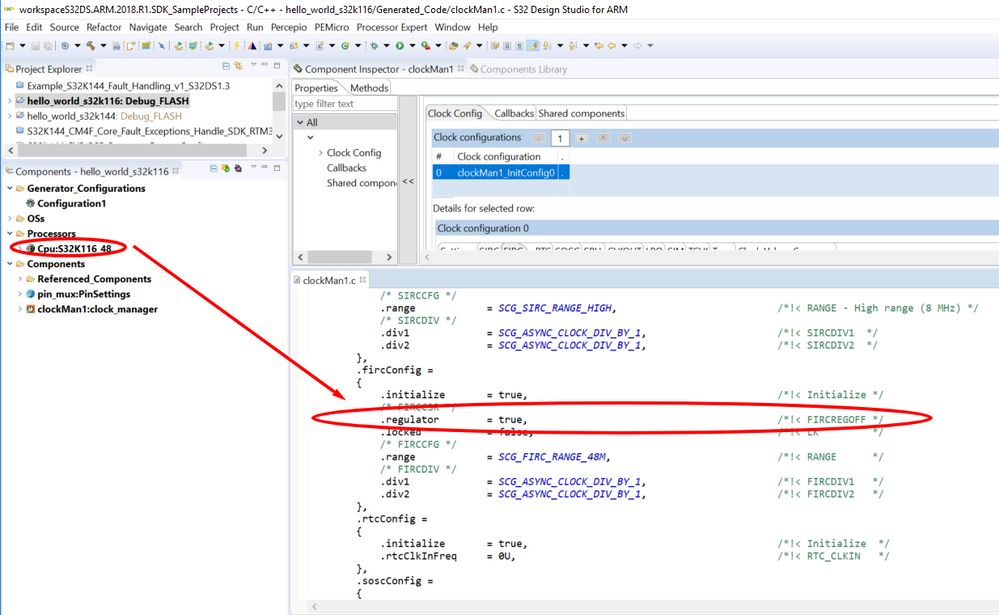

Processor Expert generated codes:

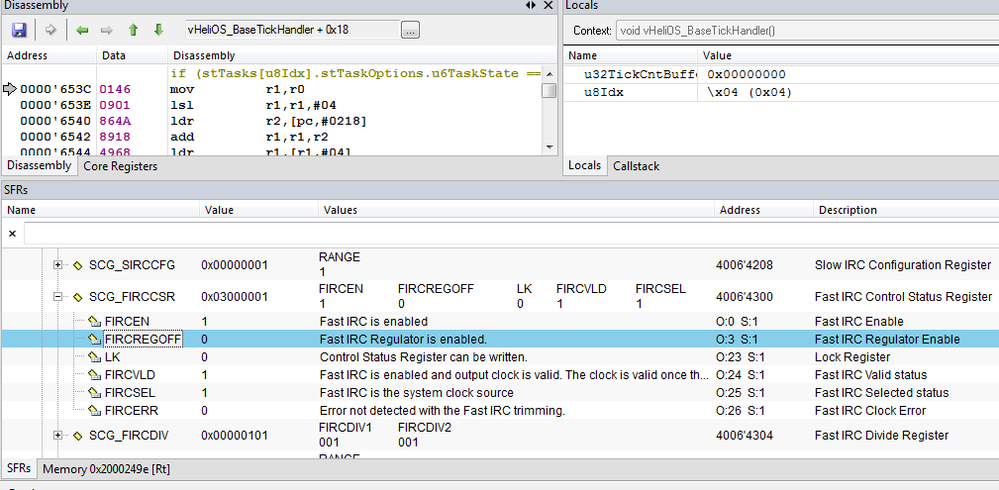

debug result:

You can check your SDK Version based on the following table:

S32K1xx SDK number | SDK Version | S32DS IDE patch/updates package |

SDK_S32K1xx_15 | S32K1xx_RTM3.0 | S32DS_ARM_v2018.R1_UP9,10(SR3.0.1) and 11(SR3.0.2) |

SDK_S32K1xx_14 | S32K1xx_BETA_2.9.2 | S32DS_ARM_v2018.R1_UP8 |

SDK_S32K1xx_13 | S32K1xx_BETA_2.9.0 | S32DS_ARM_v2018.R1_UP7 |

SDK_S32K14x_12 | S32SDK_S32K14x_RTM_2.0.0 | S32DS_ARM_v2018.R1_UP6 |

SDK_S32K14x_11 | S32K14x_BETA_1.9.0 | S32DS_ARM_v2018.R1_UP4 |

SDK_S32K14x_10 | S32SDK_S32K14x_RTM_1.0.0 | S32DS_ARM_v2.0 |

SDK_S32K14x_09 | S32SDK_S32K14x_EAR_0.8.6 | S32DS_ARM_v2.0_UP3_K14x_SDK_EAR_086/S32DS_ARM_v2018.R1 |

SDK_S32K118_10 | S32SDK_S32K118_EAR_1.8.8 | S32DS_ARM_v2018.R1_UP3 |

SDK_S32K116_00 | S32K116_EAR_1.8.7 | S32DS_ARM_v2018.R1_UP2 |

S32DS for ARM v2018.R1 IDE and S32K SDK patch/updates package download link:https://www.nxp.com/support/developer-resources/run-time-software/s32-design-studio-ide/s32-design-s...

Tips: So far, we recommend customer to use the lastest RTM version SDK for quality of EAR and Beta version SDK are not guaranteed without strict tests.

For S32K1xx, the recommended SDK version to use is S32K1xx SDK RTM3.0.0 with UP10(SR3.0.1) and 11(SR3.0.2) installed;

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ciprian Salageanu,

Thank you for the report!

Seems that the "Fast IRC Regulator" check box should rename to "Fast IRC Regulator Enable".(The description of Processor Expert is correct.)

I try to debug it, the Processor Expert configure the correct value for FIRCREGOFF bit.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Robin,

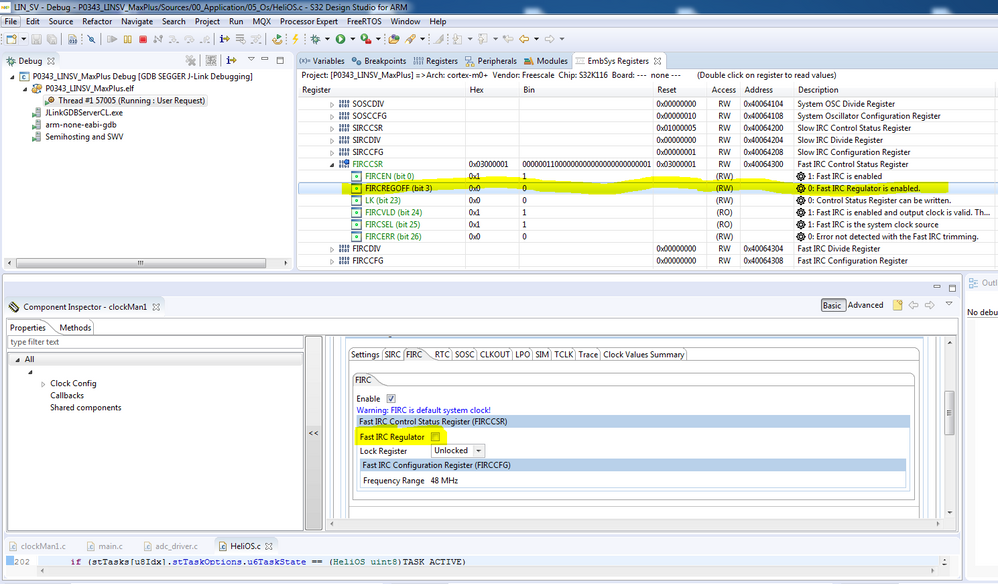

I checked with Segger j-Link debugger, I have FIRCREGOFF = 0 (=FIRC Regulator is enabled) when "Fast IRC Regulator" is unchecked in PE

Best Regards,

Ciprian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the feedback from internal team:

Could you please double check and told me which S32K SDK Version you are using?

I checked both S32K14x RTM2.0.0(not support S32K11x) and S32K1xx RTM 3.0.0, they works as expected, no bugs:

S32K144 FIRC configure tab in Processor Expert clock_manager component(both S32K1xx RTM 3.0.0 and S32K14x RTM2.0.0 are the same):

S32K116 FIRC configure tab in Processor Expert clock_manager component(S32K1xx RTM 3.0.0):

Processor Expert generated codes:

debug result:

You can check your SDK Version based on the following table:

S32K1xx SDK number | SDK Version | S32DS IDE patch/updates package |

SDK_S32K1xx_15 | S32K1xx_RTM3.0 | S32DS_ARM_v2018.R1_UP9,10(SR3.0.1) and 11(SR3.0.2) |

SDK_S32K1xx_14 | S32K1xx_BETA_2.9.2 | S32DS_ARM_v2018.R1_UP8 |

SDK_S32K1xx_13 | S32K1xx_BETA_2.9.0 | S32DS_ARM_v2018.R1_UP7 |

SDK_S32K14x_12 | S32SDK_S32K14x_RTM_2.0.0 | S32DS_ARM_v2018.R1_UP6 |

SDK_S32K14x_11 | S32K14x_BETA_1.9.0 | S32DS_ARM_v2018.R1_UP4 |

SDK_S32K14x_10 | S32SDK_S32K14x_RTM_1.0.0 | S32DS_ARM_v2.0 |

SDK_S32K14x_09 | S32SDK_S32K14x_EAR_0.8.6 | S32DS_ARM_v2.0_UP3_K14x_SDK_EAR_086/S32DS_ARM_v2018.R1 |

SDK_S32K118_10 | S32SDK_S32K118_EAR_1.8.8 | S32DS_ARM_v2018.R1_UP3 |

SDK_S32K116_00 | S32K116_EAR_1.8.7 | S32DS_ARM_v2018.R1_UP2 |

S32DS for ARM v2018.R1 IDE and S32K SDK patch/updates package download link:https://www.nxp.com/support/developer-resources/run-time-software/s32-design-studio-ide/s32-design-s...

Tips: So far, we recommend customer to use the lastest RTM version SDK for quality of EAR and Beta version SDK are not guaranteed without strict tests.

For S32K1xx, the recommended SDK version to use is S32K1xx SDK RTM3.0.0 with UP10(SR3.0.1) and 11(SR3.0.2) installed;

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin,

Thank you for answer and for extensive searches.

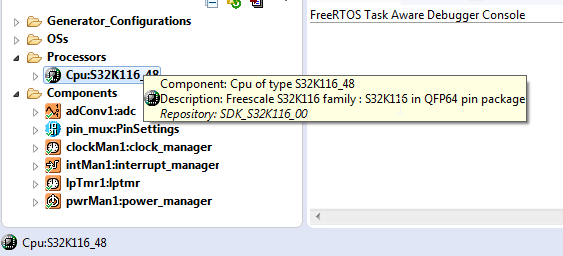

The S32K116 mask is ON96V (sorry, I did not seen this question before).

The SDK that we use is S32SDK_S32K116_EAR_1.8.7 with GreenHills compiler v2018.1.4 (I don't know if the compiler is important or not).

CPU component use in project

Since the SDK that we use is quite old now and we still can switch the SDK I will propose on my side to use the SDK that you recommended: S32K1xx RTM 3.0.0

Also with 3.0.0 SDK the issue does not reproduce - I will check on my side also.

Best Regards,

Ciprian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ciprian,

Thank you for the report, I need to consult it with internal team.

I have also try to use Segger J Link and P&E Multilink. But the value of FIRCREGOFF seems different on S32K116 and S32K144.

Would you please tell us the mask of your S32K116? I have check the S32K116 _ON96V Errata, no related bugs found.

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin,

Thanks for answer.

My MCU is S32K116, fordebug I use iSystem WinIdea 9.17.104 and IC500 (blue box) hardware adapter.

On you side (pictures) looks correct, but on my side FIRCREGOFF=0 if the box is unchecked. Please see below pictures:

With this settings in PE (box unchecked)

field FIRCREGOFF = 0 => Fast IRC Regulator is enabled conform with WinIdea debugger

Complete screen shot of debugger IDE.

Seems that the Debuggers shows us different values in the FIRCCSR registers. I have one more debugger from other company I can try to see what values get with that one.

Also the micro controller is different on my side.

Best Regards,

Ciprian