- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 产品论坛

- :

- PowerQUICC处理器

- :

- CW 8.8: Could not set PC to entry point.

CW 8.8: Could not set PC to entry point.

I am using MPC 860 processor. I could not able to debug the code with Code warrior USB TAP. Getting an error "Could not set PC to entry point". But unable to correct this. Anybody is there to help?

Thank you

Best regards

Mahesh

已解决! 转到解答。

Incorrect XFC connection produces incorrect SPLL behavior. It produce incorrect BDM or JTAG behavior. See the Section 14.2.2.3 of the MPC860 User's Manual:

https://www.nxp.com/docs/en/reference-manual/MPC860UM.pdf

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Check TRST connection on your board.

The TAP signals must be configured as follows to reset the scan chain logic: If both the TAP and low power mode are never used, connect TRST to ground. If the TAP or low power mode is used, connect TRST to PORESET. If power down mode (the lowest power mode, where VDDH is disabled) is used, connect TRST to PORESET through a diode (anode to TRST, cathode to PORESET). The TRST has internal pull-up resistor. Typical value of this resistor is about 5kOm but can vary by approximately a factor of 2.

Is there problem for connection if the MPC860FADS board is used?

Is there possibility to test your board and USB TAP under Windows XP?

Have a great day,

Pavel Chubakov

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

CodeWarrior 8.8 uses the MPC860 BDM interface for connection to the MPC8xx.

Do you use CodeWarrior 8.8 and the MPC860 BDM for debugging?

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

The DBGC field of the MPC860 Hard Reset Configuration is used for pin assigning of the IP_B[0–1]/IWP[0–1]/VFLS[0–1] pins. See the Table 11-3 of the MPC860 User's Manual.

The VFLS[0-1] signals of the BDM connector on the MPC8XXFADS board usually are connected to FRZ pin of MPC.

VFLS and FRZ signals are used to indicate debug mode of the processor. When both VFLS(0:1) are at '1', the MPC is in debug mode.

If FRZ is set, the MPC is in debug mode.

Check the SIUMCR[DBPC] value .

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

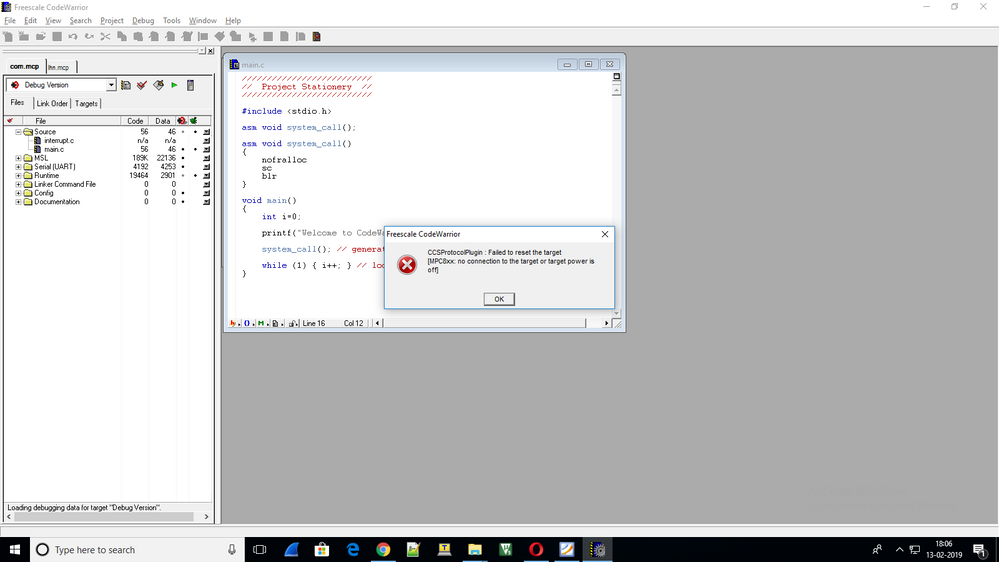

When we are trying to enter into debug mode that time we are getting the JTAG clcok ,TDI,TDO and reset also then we are getting the error as failed to reset the target .The error is attached below .

Thank you for the reply.

The data pins of the external bus are connected PULL UP of 3.3volts supply with the 4.7k resistor. But in the development board they are connected to the CPLD is this makes any difference .Now also we are getting the same error as explained in the above .Whether VFLS[0,1] are in the control of the processor or with the external events(user controlled ).

Incorrect XFC connection produces incorrect SPLL behavior. It produce incorrect BDM or JTAG behavior. See the Section 14.2.2.3 of the MPC860 User's Manual:

https://www.nxp.com/docs/en/reference-manual/MPC860UM.pdf

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thank you for the reply. How to make this processor to work.Now we are trying to pull down the VDDSYN pin to disable the SPLL . Now the processor is running with low frequency (according to the user manual section 14.2.2.4 ) working with JTAG mode or not . One more observation we made that is VFLS0 AND VFSL1 are in the low but according to the user manual these two pins must be high right . But in our design we getting above mentioned pins in low state what may be the problem . Can you please suggest us in this regard.

Best regards

Mahesh

Test your CodeWarrior TAP using static IP. See CodeWarrior TAP User Guide:

https://www.nxp.com/docs/en/user-guide/CWTAPUG.pdf

See simple example below.

- Set new static IP

core> netparam static_ip_address 192.168.3.111

core> netparam bootconfig static:lab01 // lab01 - it is name. you can set different name

core> reset

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thank you for the reply. In the hardware design we are not connected the XFC pin to any where left open . But in the reference design this pin is connected to a capacitor with the VDDSYN supply.In the data sheet they mentioned that the External filter capacitor for the PLL circuitry. Whether this will make any error towards JTAG debug.

Best regards

Mahesh

Test CCS connection to your board using the following commands in CCS console:

(bin) 49 % config cc cwtap

(bin) 50 % show cc

The following commands also can be used:

(bin) 49 % log v

(bin) 50 % source IDcode.tcl

Is there connection to the CodeWarrior TAP and MPC860 if these commands are used?

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

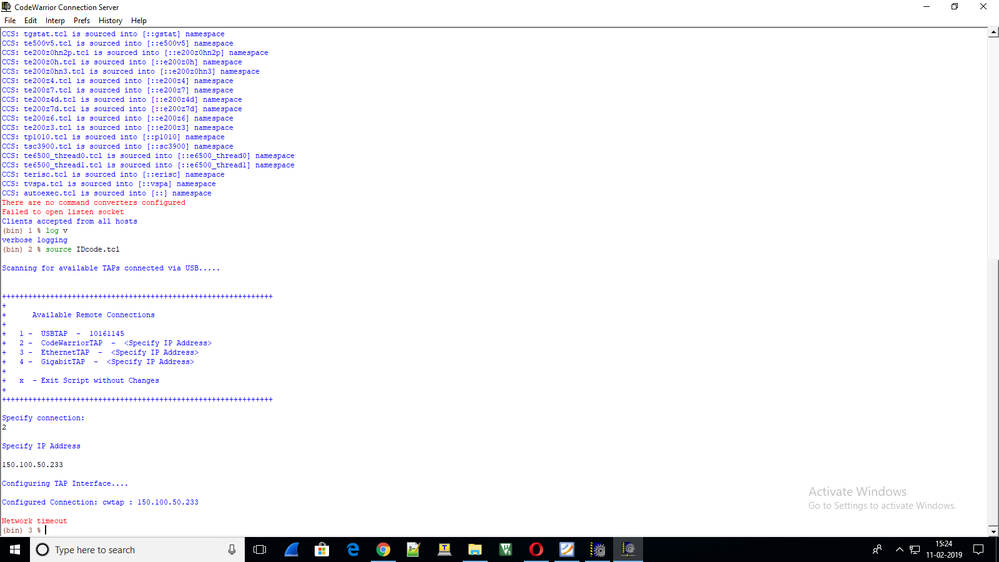

i have checked at ccs.exe by using the above commands ,

after selecting the device and entering ip address of the pc, it is showing connection network timeout. please check the image and help us.

Usually similar error message happens if "Software Patch: CW PA v8.8.6 Windows " is not installed". See the following page:

https://nxp.flexnetoperations.com/control/frse/download?agree=Accept&element=6121541

This patch installs driver for CodeWarrior TAP.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------