- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Dear Saint,

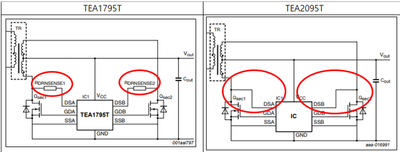

1. Resistors in series with the drain are not necessary and not recommend when using the TEA2095. The TEA2095 has different internal IC circuitry connected to the DSA and DSB pins. Adding resistors can even degrade the regulation of the adaptive gate drive due to a voltage offset because of small currents flowing into the DSA and DSB pins.

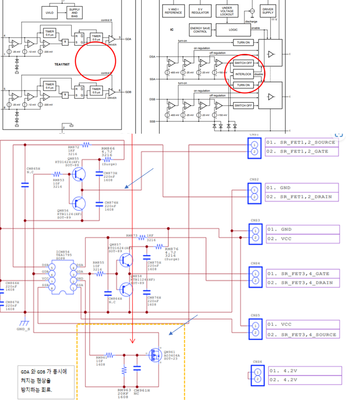

2. The interlock delay time function has a typical value of 200ns. The push / pull circuits will add a switch-on and switch-off delay time to both outputs. When the switch-on delay time and switch-off delay time of the push / pull circuit are the same, then it will not have an effect on the delay / none-overlap time. If the switch-off time of the push / pull circuit is longer than the switch-on delay time, then the resulting delay / none-overlap time will be shorter. Measuring the timing with an oscilloscope can be used to find what exactly the effect of the push / pull circuit is on the delay time.

Best regards,

Tomas

Hi Tomas,

Your feedback is very valuable as for me. Thanks a lot!

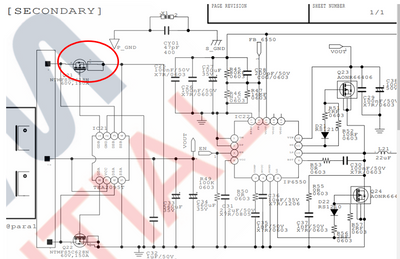

BTW, SR FET Drain-source voltage exceeds 60V when we connect buck-USB PD evk board made by INJOINIC. Our EVK FET Vds is 60V grade so we disconnect buck-USB PD evk then Vds is 51V.

Looks there is no mis-probing. How is your idea on this phenomenon?

BR/Saint

Dear Saint,

1. Resistors in series with the drain are not necessary and not recommend when using the TEA2095. The TEA2095 has different internal IC circuitry connected to the DSA and DSB pins. Adding resistors can even degrade the regulation of the adaptive gate drive due to a voltage offset because of small currents flowing into the DSA and DSB pins.

2. The interlock delay time function has a typical value of 200ns. The push / pull circuits will add a switch-on and switch-off delay time to both outputs. When the switch-on delay time and switch-off delay time of the push / pull circuit are the same, then it will not have an effect on the delay / none-overlap time. If the switch-off time of the push / pull circuit is longer than the switch-on delay time, then the resulting delay / none-overlap time will be shorter. Measuring the timing with an oscilloscope can be used to find what exactly the effect of the push / pull circuit is on the delay time.

Best regards,

Tomas