- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

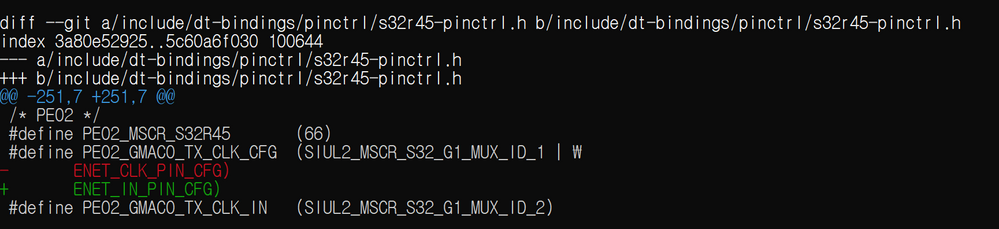

s32r45's gmac default is 'rgmii' so that gmac0 tx clock is currently output.

We should change tx clock as input in order to use 'mii'

Accordingly, s32r45-pinctrl.h file has been changed as follow

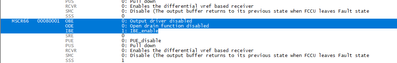

In T32, modification above is not applied to register

Any advice?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eddy,

I just tried this out on BSP32 and it seems to work:

The change you made is exactly the one I did on Uboot:

diff --git a/include/dt-bindings/pinctrl/s32r45-pinctrl.h b/include/dt-bindings/pinctrl/s32r45-pinctrl.h

index 3a80e52925..5c60a6f030 100644

--- a/include/dt-bindings/pinctrl/s32r45-pinctrl.h

+++ b/include/dt-bindings/pinctrl/s32r45-pinctrl.h

@@ -251,7 +251,7 @@

/* PE02 */

#define PE02_MSCR_S32R45 (66)

#define PE02_GMAC0_TX_CLK_CFG (SIUL2_MSCR_S32_G1_MUX_ID_1 | \

- ENET_CLK_PIN_CFG)

+ ENET_IN_PIN_CFG)

#define PE02_GMAC0_TX_CLK_IN (SIUL2_MSCR_S32_G1_MUX_ID_2)

/* PE03 */

- I just rebuild uboot:

make s32r45evb_defconfig

make CROSS_COMPILE=/<To toolchain path>/gcc-arm-10.2-2020.11-x86_64-aarch64-none-linux-gnu/bin/aarch64-none-linux-gnu-

- Rebuild ATF:

make CROSS_COMPILE=/<To toolchain path>/gcc-arm-10.2-2020.11-x86_64-aarch64-none-linux-gnu/bin/aarch64-none-linux-gnu- ARCH=aarch64 PLAT=s32r45evb BL33=/<To Uboot Path>/u-boot/u-boot-s32.bin

- And flashed the fip.s32

sudo dd if=fip.s32 of=/dev/mmcblk0 skip=512 seek=512 iflag=skip_bytes oflag=seek_bytes conv=fsync,notrunc

If you are following these steps it is likely that the image is not being updated.

Saludos,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks. It was my miss. I works well

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eddy,

I just tried this out on BSP32 and it seems to work:

The change you made is exactly the one I did on Uboot:

diff --git a/include/dt-bindings/pinctrl/s32r45-pinctrl.h b/include/dt-bindings/pinctrl/s32r45-pinctrl.h

index 3a80e52925..5c60a6f030 100644

--- a/include/dt-bindings/pinctrl/s32r45-pinctrl.h

+++ b/include/dt-bindings/pinctrl/s32r45-pinctrl.h

@@ -251,7 +251,7 @@

/* PE02 */

#define PE02_MSCR_S32R45 (66)

#define PE02_GMAC0_TX_CLK_CFG (SIUL2_MSCR_S32_G1_MUX_ID_1 | \

- ENET_CLK_PIN_CFG)

+ ENET_IN_PIN_CFG)

#define PE02_GMAC0_TX_CLK_IN (SIUL2_MSCR_S32_G1_MUX_ID_2)

/* PE03 */

- I just rebuild uboot:

make s32r45evb_defconfig

make CROSS_COMPILE=/<To toolchain path>/gcc-arm-10.2-2020.11-x86_64-aarch64-none-linux-gnu/bin/aarch64-none-linux-gnu-

- Rebuild ATF:

make CROSS_COMPILE=/<To toolchain path>/gcc-arm-10.2-2020.11-x86_64-aarch64-none-linux-gnu/bin/aarch64-none-linux-gnu- ARCH=aarch64 PLAT=s32r45evb BL33=/<To Uboot Path>/u-boot/u-boot-s32.bin

- And flashed the fip.s32

sudo dd if=fip.s32 of=/dev/mmcblk0 skip=512 seek=512 iflag=skip_bytes oflag=seek_bytes conv=fsync,notrunc

If you are following these steps it is likely that the image is not being updated.

Saludos,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I have asked our R45 application engineer for help.

Once I have any answer I will feedback you.

Best regards,

Peter