- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

TJA1101 sleep\wake up issue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi guys,

I'm working with TJA1101 connected with Fs6500 following connection.png.

- PHYAD1 is pulled to Vaux (3.3v) of Fs6500.

- PHYAD2 is pulled to GND.

- The PORST pin of MCU and RST_N pin of TJA1101 is connected to The RSTB pin of Fs6500.

- VDD(io) of TJA1101 is connected to Vaux of Fs 6500.

I'm having an issue with the Phy wasn't able to wake up after I triggered to sleep and wake up the whole system with the Fs6500 and I also observed a strange behavior of pin strapping.

Step to reproduce:

1) Open the KEY_SW and request the SPI command to make Fs6500 go to LPOFF - SLEEP mode (the MCU will be off after that). The TJA1101 went to sleep mode since Undervoltage was detected.

2) Wake the whole system by closing the KEY_SW.

3) Wake the Phy by sending the standby mode command with PHYAD[4:0] = 0b00010 (following the pin strapping configuration) at MCU initialization.

Expected result:

The Phy should be able to wake up and be in normal mode.

Actual result:

The Phy wasn't able to wake up.

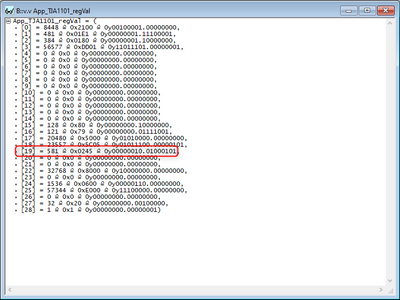

4) After step 3), I read all registers of TJA1101A using PHYAD[4:0] = 0b00000 and observed that the PHYAD[4:0] was 0b00000 ( step4.png)

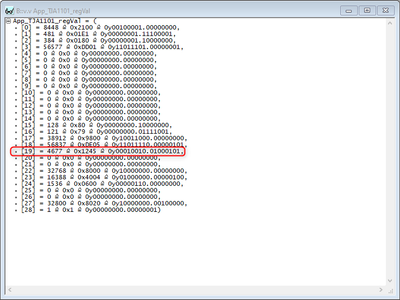

5) I woke the Phy by sending the standby mode command with PHYADD[4:0] = 0b00000. The Phy was able to wake up, but it seems like somehow the strap-pin was performed and the PHYADD[4:0] had the value 0b00010 after that. ( step5.png)

Could anyone help me to explain this strange behavior?

Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

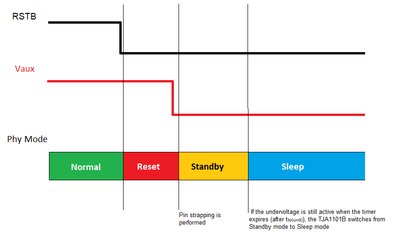

It looks like pin strapping does not happen in your case at step 3. Note, if you apply VBAT only (no 3.3V supplies), the device will tranfer to sleep mode without pin strapping event. As soon as 3.3V applied, it is not possible to wake up the device using 0b00010 address because it (strapping configuration) has not been sampled yet. As soon as pin strapping occurs, address 0b00010 becomes functional.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your answer,

Yes, you're right, The pin strapping should not happen at step 3), but the PHYAD[4:0] was 0b00010 before I triggered to sleep the system with the Fs6500.

Because of that, I expected that I could be able to wake the Phy with the PHYAD[4:0] = 0b00010. Sadly, It didn't happen.

The picture below is the register value before the system went to sleepmode. (before step 1)

So I wonder that why the value of PHYAD[4:0] was 0b00000 After I woke the system and why I could not wake the Phy with the PHYAD[4:0] = 0b00010 ...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Is it possible that the MCU drives reset (PORST) when the system goes to sleep?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, in theory, when the low-power mode was requested to the SBC, the SBC released the RSTB pin (went to low level) before switching off the Vaux and they will be at the high level again after ECU woke up. Is there a connection that could lead to the change of the PHYAD?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

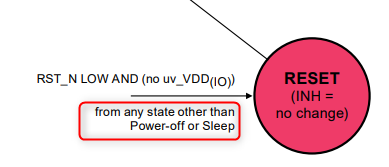

Yes, RST signal resets configuration of the TJA, so previous strapping setup is lost.

Note, PHY address 0x0 is not "new" or reset address, it is always there. If you set the address to e.g. 0x2 during pin strapping, address 0x0 is still applicable. If you have a single PHY on the SMI, you can use address 0x0 permanently.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Possible scenario can be as following:

1. RSTB signal low resets the PHY but pin strapping does not happen because 3.3V immediately disappears (pin strapping can not happen without 3.3V supply). As a result the PHY goes to sleep mode after Tto(uvd) without configuration, i.e. reset sequence does not complete.

2. As soon as 3.3V applies and you wake up the PHY (using address 0x0), it runs pin strapping due to previous reset event, so completes reset sequence.