- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- RFID / NFC

- :

- NFC

- :

- Re: Issue with the Waterlevel interrupt

Issue with the Waterlevel interrupt

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Issue with the Waterlevel interrupt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Let me start by giving some idea about the HIF configuration. Below are connections of PN7462 with the FTDI232 chip.

PN7462 ----------- FTDI232

TX <---------> RX

RX <---------> TX

GPIO_2 <---------> CTS

CTS <---------> RTS

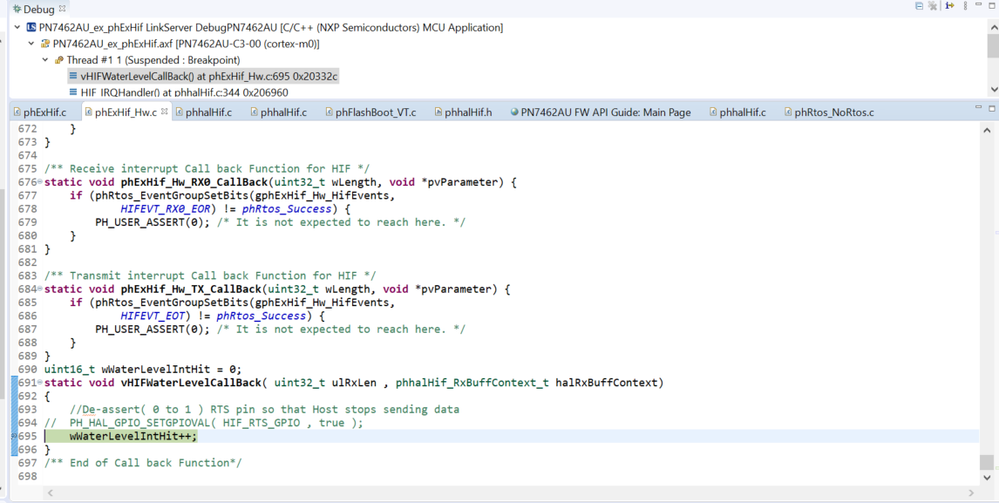

Now the Waterlevel is configured at 240. and Rx buffer size is 248. When Waterlevel interrupt is generated, GPIO_2 in transit from 0->1. Which will make FTDI232 stop sending data. Now when I transfer 320KB of data I am seeing an overflow error in ErrorCallback. after debugging I found that when I get an overflow error GPIO_2 is low means the Waterlevel interrupt has not been Hit. I have verified the same in debug mode by putting a counter. in Rx callback and Waterlevel callback. I am attaching the HIF section for reference.

I am also attaching a debug window from which I have driven this conclusion. As you can see when an overflow error has occurred. the Waterlevel hit count() and Rxcallback hit count() are the same it means more than 248 bytes are received but the Waterlevel callback has not been hit and Error callback is called. What could be the reason behind the Waterlevel interrupt not generating. Let me know if more information is required.

Thanks, Jayesh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Kan_Li Thanks for the response.

I believe it is Enabled as I am getting the Recieve End callback interrupt. But I am unable to find Register you are referring to. Can you please point out which register or register Bit I have to configure for Enabling HOST_IF?

Thanks in advance.

Jayesh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jayesh_joshi ,

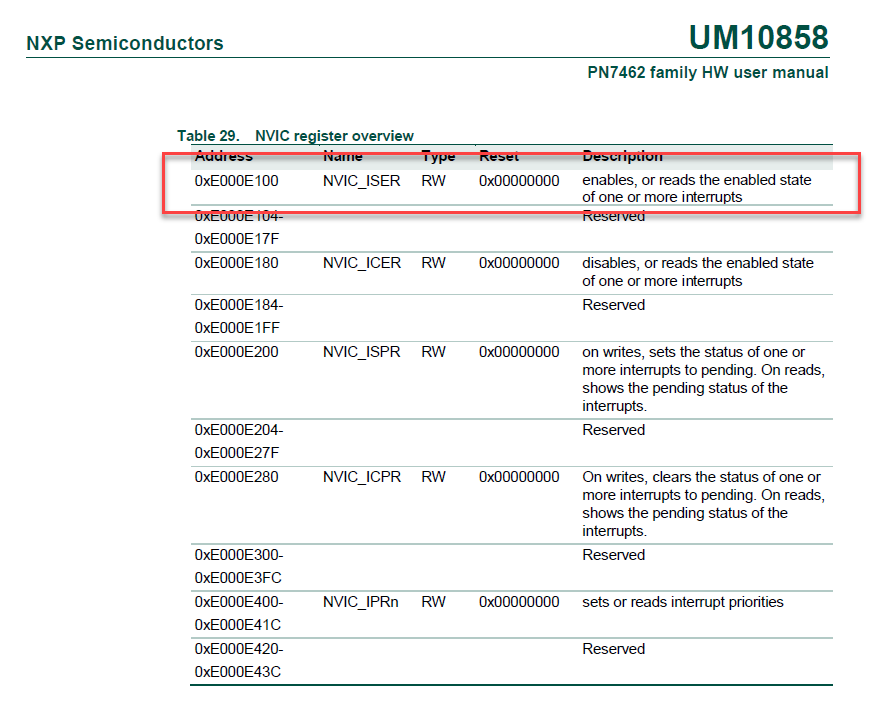

Please kindly check the following register on your side.

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @jayesh_joshi ,

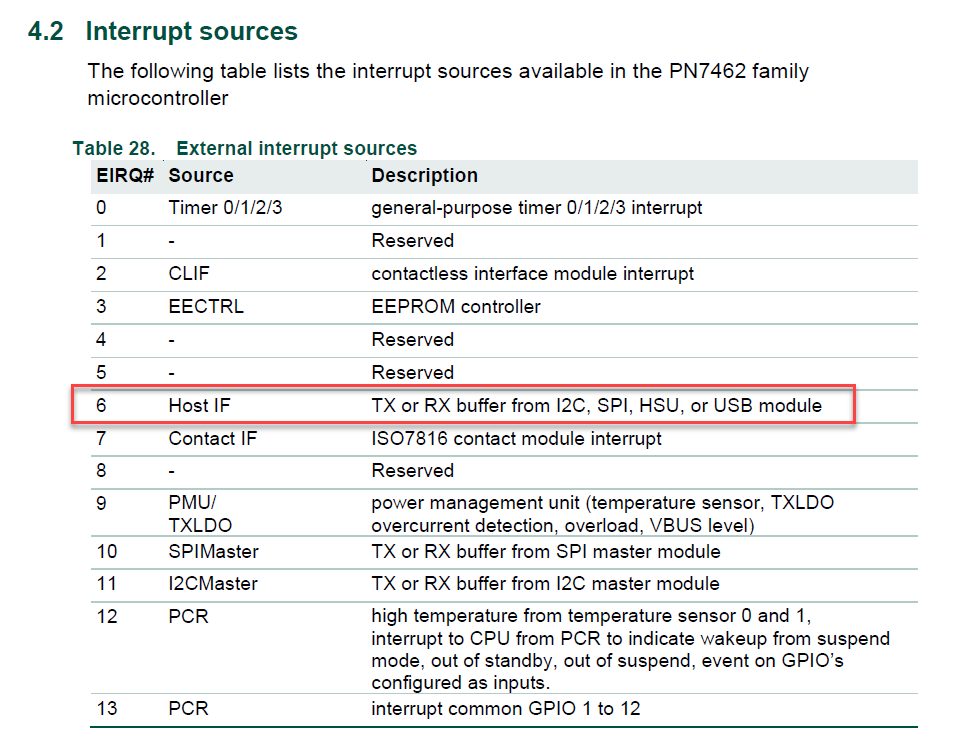

Thanks for the information! I have noticed you enable the waterlevel interrupt of HSUART, but didn't find where you enable the Host IF interrupt of NVIC. Would you please clarify? Please kindly refer to the following for more details.

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Kan_Li

I have tried setting HIF Intruppt by adding the below line HIF init API. But still, the issue persists.

/* Enable the Host Interface Input */

PH_REG_SET_BIT(HOSTIF_CONTROL_REG, HIF_ENABLE);

phHal_Nvic_EnableInterrupt( 1<<6 );

Regards Jayesh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jayesh_joshi ,

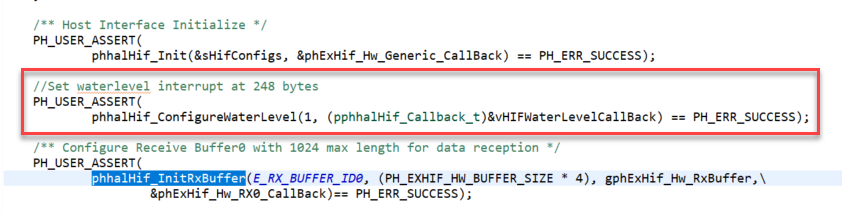

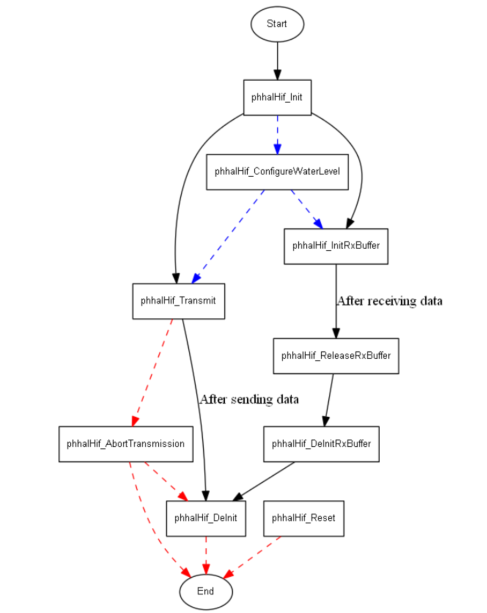

I tried to reproduce your issue here but it works as expected. I built the test code based on phExHif demo, just put phhalHif_ConfigureWaterLevel() right before phhalHif_InitRxBuffer() as described in the API guide.

and the callback was hit right after 1 byte sent out.

You may refer to the API guide or the following for more details.

Hope that helps,

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the response.

You won't be able to see issues in small data transfers. I am facing an issue when I transfer 300kb of data and only 1-2 times waterlevel interrupt is not hitting. Also, this 300kb of data is going to Reader Writer to Card Emulator device over NFC so there is like NFC data transfer also happening and that could be the reason for waterlevel interrupt not getting generated. Maybe you can help me to debug if that could be the reason.

Regards Jayesh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jayesh_joshi ,

Actually it looks like an application issue than a silicon issue, you know, the CLIF interrupt has higher priority than the host IF interrupt, so in some cases when the CLIF interrupt is handling something, the waterlevel interrupt might be set in the same time but the host IF interrupt has to be pending, it is not a good way to set a higher priority for the host IF interrupt, as it might lead to some timing issue from the NFC communication, so better follow the expert's recommendation that I posted in your previous thread: https://community.nxp.com/t5/NFC/How-to-drive-ATX-C-RTS-pin-high-in-PN7462/m-p/1152380#M7662 , Best would be to set the rx buffer size bigger as the expected maximum frame size. Multipe rx buffers can be used to operate in a parallel way.

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------