- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

init MMU on MPC55XX

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello.

I have a little problem with writing internal memory on MPC55XX,

I wrote two bootloaders, one for BAM mode, one for RAM .

for BAM the bootloader works great.

for RAM the bootloader cannot erase low Blocks,

mid and high Blocks are no problem.

I load the RAM bootloader on the CAN bus.

I tried to initialize MMU, but it doesn't lead to anything,

help please find the problem, what am I doing wrong?

maybe some other settings are needed?

Thanks!

lowEnabledBlocks = 0x1;

midEnabledBlocks = 0x00000000;

highEnabledBlocks = 0x00000000;

returnCode = pFlashErase (&ssdConfig, shadowFlag, lowEnabledBlocks,

midEnabledBlocks, highEnabledBlocks, NULL_CALLBACK );

if ( H7F_OK != returnCode )

{

ErrorTrap(returnCode);

}

asm void MMU_Set_TLB1(void) {

lis r3, 0x1001

mtMAS0 r3

lis r3, 0xC000

ori r3, r3, 0x0500

mtMAS1 r3

lis r3, 0x0000

mtMAS2 r3

lis r3, 0x0000

ori r3, r3, 0x003F

mtMAS3 r3

msync

tlbwe

isync

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alexander,

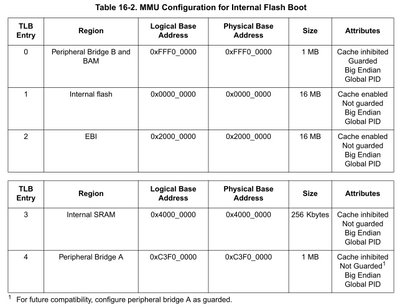

I don't think there's problem with MMU. In case of internal boot mode or serial boot mode, the MMU is initialized by BAM in this way which should be sufficient:

It would require more debugging. Did you confirm the low blocks are unlocked in both LMLR and SLMLR registers? What is the content of FLASH_MCR registers after unsuccessful erase/program operation?

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi Lukas,

thanks for the help.

i read MMU tlb,

10000000 C0000300 00000000 0000003F

10010000 C0000300 00010000 0001000F

10020000 C0000300 00020000 0002003F

10030000 C0000300 00080000 0008003F

10040000 C0000300 00090000 0009003F

10050000 C0000300 000A0000 000A003F

10060000 C0000200 000B0000 000B003F

10070000 C0000200 000B4020 000B403F

trying to fix the first tlb,

but it doesn't help, there is still no access, maybe need some other settings to update the MMU?

asm void MMU_Set_TLB1(void) {

lis r3, 0x1001

mtMAS0 r3

lis r3, 0xC000

ori r3, r3, 0x0300

mtMAS1 r3

lis r3, 0x0001

mtMAS2 r3

lis r3, 0x0001

ori r3, r3, 0x003F

mtMAS3 r3

msync

tlbwe

isync

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I would need more details. What I can see - first descriptor covers first 64KB of flash. It corresponds to flash blocks L0 and L1 in partition 1. It's configured as BOOK E page and it's cacheable. All accesses are permitted. What do you want to change?

By the way, this excel configurator could help you:

https://community.nxp.com/t5/MPC5xxx-Knowledge-Base/MMU-Assist-Register-CONFIGURATOR/ta-p/1110436

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi

I don't know what else can be done.

after trying to write a flash, the internal flash is not readable, is it blocked?

when trying to read flash, the processor is immediately reset.

Shadow flash is readable without problems.

maybe other settings are needed?

Thank you!

FLASH_MCR C3F88000 0B603600

FLASH_LMLR C3F88004 800CFFC0

FLASH_HLR C3F88008 8FF00000

FLASH_SLMLR C3F8800C 800CFFC0

FLASH_LMSR C3F88010 00000000

FLASH_HSR C3F88014 00000000

FLASH_AR C3F88018 0001FFF8

FLASH_BIUCR C3F8801C 00054BF1

FLASH_BIUAPR C3F88020 000000FF

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

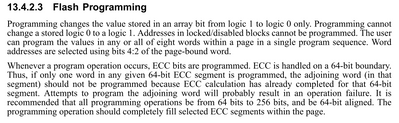

MMU configuration seemed to be correct, so you can read the flash anytime. If not, it could be caused by ECC errors. ECC error can occur if erase operation is terminated by unexpected reset, so the flash is left in undetermined state or due to overprogramming when you program double word (64bits) which are not fully erased.

You can check the content of memory in your debugger. If you see in the memory window something like "XX" or "??" then the debugger can't read the flash due to ECC errors (most likely).

The solution - erase the flash again. If you see that all the flash blocks are in erased state (0xFF) then ECC was the root cause.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi lukas!

I erased the internal flash in BAM mode, now it is readable.

yes i have ECC error 02 after FlashInit_Unlock, i do clear FLASH_MCR-EER bit.

could it be due to the eeprom in the internal flash?

I took another MPС5566, same problem, for BAM the bootloader works great.

for RAM the bootloader cannot erase low Blocks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

this would require more debugging, I have no idea what you do in the code. Clearing of EER is not enough, this clears the flag only. But the error is still present in the flash. If you use the flash as EEPROM, your application should be prepared for ECC errors - the exceptions should be handled appropriately. You can take a look at:

https://www.nxp.com/docs/en/application-note/AN5200.pdf

https://www.nxp.com/docs/en/application-note-software/AN5200SW.zip

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi

Thank you.

does this line of processors have erase - protections?

maybe it was closed for writing LOW_BLOCK0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The only protection is given by LMLR and SLMLR registers.

You mentioned these values:

FLASH_LMLR C3F88004 800CFFC0

FLASH_SLMLR C3F8800C 800CFFC0

... so, the low and mid blocks are enabled for erase and write.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I just don't understand why this code works in BAM mode, but not in RAM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

what can I check to find out what the problem is?

what parameter? register?

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

what can you see in the debugger? Where does it crash exactly? Which operation/command? Is an exception triggered?

Regards,

Lukas