- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

With MPC5676R, Optimization() function has malfunction

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I'm using MPC5676R with trace32,

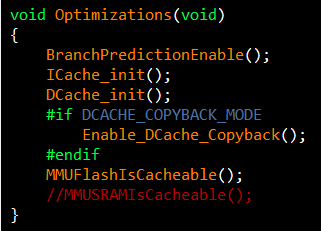

The example code "XPC567XRKIT-PinToggleStationery-V0_7" has optimization.c and optimization.h files.

when OPTIMIZATIONS_ON = 1 , Optimizations() function will be executed to enable cache.

but, When I call the MMUSRAMIsCacheable(), the operation is weird.

I can't change any member variables of struct, but other global variables can be changed in trace32 WATCH window.

I thought that the code in MMUSRAMIsCacheable() function is wrong, but I don't know what it does mean.

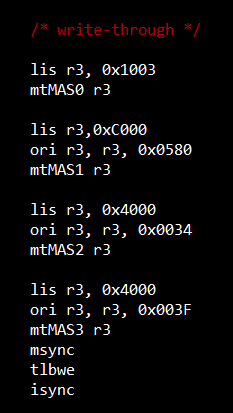

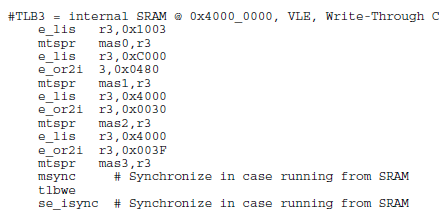

In AN4324, the SRAM code is different with the example MMUSRAMsCacheable() code.

When I change the code according to AN4324, It does not affect.

What is the reason about these phenomenon?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

- does the write access fail while core running, halted or both?

- how does it fail? E.g. error message?

- is macro DCACHE_COPYBACK_MODE also set?

- what is the address of the failing access?

Regards,

Reinhard

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello~

-The write access is successful when core is halted, but not running.

so I have to pause to change values

- It dose not alert error message

- DCACHE_COPYBACK_MODE is disabled, it must be write through method

- How can I see the address of the access?

Regards,

jaehak Kim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please try with

SYStem.Option NexusMemoryCoherency ON

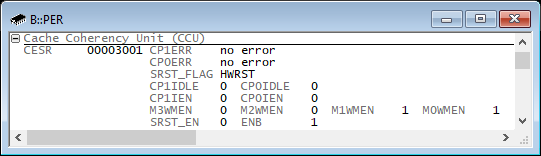

On MPC5676R and MPC5777C, this setting willconfigure the debugger to tell the CCU that the caches have to be snooped for this the memory access. This setting is only allowed if the processor is configured to write-through mode, like in your case.

Best regards,

Reinhard

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your response!

But It does not work.

The command button does not appear in system window and I cannot think it was taken effect

when I input the command in command window.

Regards,

Jaehak Kim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please check if the application set up the CCU. It should be configured this way:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I just checked it and I don't see any issue.

I guess it could have something to do with access class attributes in the TRACE32 setting. Try to investigate

If you show me specific case when the issue happens I could try it here.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK I'll check it, thanks :smileyhappy: