- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Shutdown self-test problem!

Shutdown self-test problem!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all:

we have found a strange situation, we test our source code on board with different versions of MPC5744P, the result is different .

our program can not working normal on our board (with chip mask IN15P), there always have three low blocks are failed . But it can work on our old board (with chip mask IN65H) .

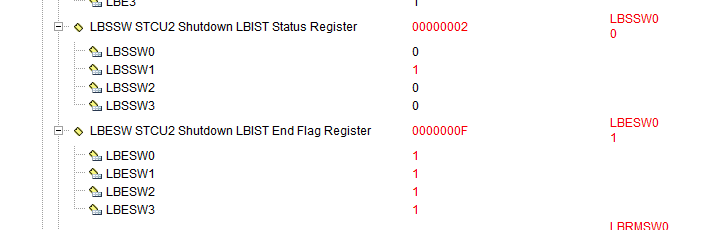

the result is still like this on our B2 sample (chip mask IN15P):

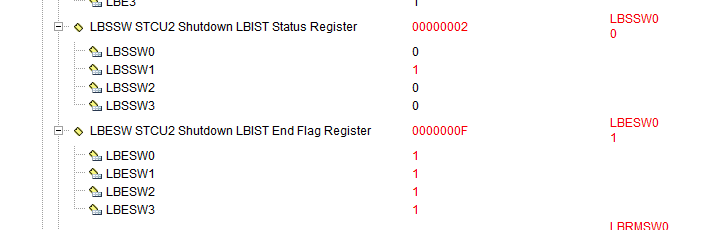

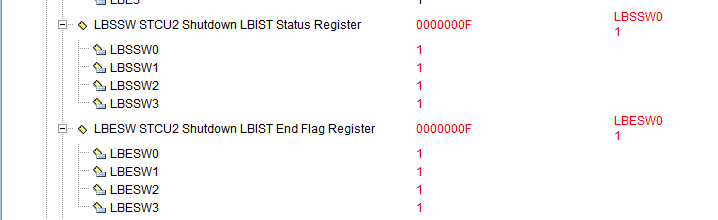

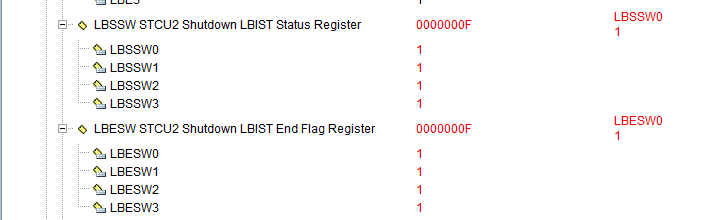

but the results on our old sample - B1(chip mask IN65H):

why this is happen ? how can we fix it ?

this is our shutdown self-test code:

void ShutDownSelfTest()

{

if (STCU_MBELSW!=0x07ffffff)

{

Pre_ShutDownSelfTest();

ShutDownSelfTest_Init();

}

sys_check_stcu_shutdown();

}

/*----------------------------------------------------------------------*/

/* */

/* check shutdown selftest status */

/* */

/*----------------------------------------------------------------------*/

static void sys_check_stcu_shutdown()

{

/*Shutdown LBIST End Flag*/

while(STCU_LBESW !=0x0000000f );

/*Shutdown LBIST Status*/

while(STCU_LBSSW != 0x0000000f);

/*Shutdown MBIST End Flag*/

while (STCU_MBELSW !=0x07ffffff);

/*MBIST Status Low Register*/

while(STCU_MBSLSW !=0x07ffffff );

}

/*----------------------------------------------------------------------*/

/* */

/* Init system registers for shutdown selftest */

/* */

/*----------------------------------------------------------------------*/

static void Pre_ShutDownSelfTest()

{

/* 1. End the currently running application, including graceful termination of

peripheralsas required by the application */

/* 2. Configure FlexRay and CAN clock sources and divider for self-test:*/

MC_CGM.AC1_DC0.B.DE = 1;

MC_CGM.AC1_DC0.B.DIV = 1;

FR_0.MCR.B.CLKSEL=1;

CAN_0.CTRL1.B.CLKSRC=1;

CAN_1.CTRL1.B.CLKSRC=1;

CAN_2.CTRL1.B.CLKSRC=1;

/* 3. Ensure PBRIDGE clock is not over clocked (maximum frequency is 50MHz) when SYS_CLK is switched to 200MHz. */

MC_CGM.SC_DC0.B.DIV = 3;

/* 4. Configure DRUN to turn off PLL1 (to save power), turn off PLL0 so PLL0 can bere-configured for the required 200MHz self-test clock frequency, turn on the XOSC

as it is needed to provide the PLL0 reference clock during self-test, and select IRCOSC to source SYS_CLK: */

MC_ME.DRUN_MC.B.SYSCLK=0;/*Select IRCOSC as the SYS_CLK clock source*/

MC_ME.DRUN_MC.B.XOSCON=1;/*Enable XOSC*/

MC_ME.DRUN_MC.B.PLL0ON=0;/*Disable PLL0:*/

MC_ME.DRUN_MC.B.PLL1ON=0;/*Disable PLL1*/

/*Gate off all peripheral clocks because they should not be running: */

MC_ME.RUN_PC[0].B.DRUN =0;

MC_ME.RUN_PC[1].B.DRUN =0;

MC_ME.RUN_PC[2].B.DRUN =0;

MC_ME.RUN_PC[3].B.DRUN =0;

MC_ME.RUN_PC[4].B.DRUN =0;

MC_ME.RUN_PC[5].B.DRUN =0;

MC_ME.RUN_PC[6].B.DRUN =0;

MC_ME.RUN_PC[7].B.DRUN =0;

MC_ME.PCTL9.B.RUN_CFG=0;

MC_ME.PCTL11.B.RUN_CFG=0;

MC_ME.PCTL12.B.RUN_CFG=0;

MC_ME.PCTL30.B.RUN_CFG=0;

MC_ME.PCTL36.B.RUN_CFG=0;

MC_ME.PCTL38.B.RUN_CFG=0;

MC_ME.PCTL77.B.RUN_CFG=0;

MC_ME.PCTL78.B.RUN_CFG=0;

MC_ME.PCTL79.B.RUN_CFG=0;

MC_ME.PCTL91.B.RUN_CFG=0;

MC_ME.PCTL98.B.RUN_CFG=0;

MC_ME.PCTL99.B.RUN_CFG=0;

MC_ME.PCTL104.B.RUN_CFG=0;

MC_ME.PCTL107.B.RUN_CFG=0;

MC_ME.PCTL124.B.RUN_CFG=0;

MC_ME.PCTL126.B.RUN_CFG=0;

MC_ME.PCTL137.B.RUN_CFG=0;

MC_ME.PCTL141.B.RUN_CFG=0;

MC_ME.PCTL144.B.RUN_CFG=0;

MC_ME.PCTL146.B.RUN_CFG=0;

MC_ME.PCTL204.B.RUN_CFG=0;

MC_ME.PCTL208.B.RUN_CFG=0;

MC_ME.PCTL209.B.RUN_CFG=0;

MC_ME.PCTL214.B.RUN_CFG=0;

MC_ME.PCTL235.B.RUN_CFG=0;

MC_ME.PCTL237.B.RUN_CFG=0;

MC_ME.PCTL239.B.RUN_CFG=0;

MC_ME.PCTL245.B.RUN_CFG=0;

MC_ME.PCTL247.B.RUN_CFG=0;

MC_ME.PCTL251.B.RUN_CFG=0;

MC_ME.PCTL255.B.RUN_CFG=0;

/* 5. Activate new configuration by performing mode change to DRUN: */

// MC_ME.MCTL.B.TARGET_MODE = 3;

MC_ME.MCTL.R = 0x30005AF0; /* Mode & Key */

MC_ME.MCTL.R = 0x3000A50F; /* Mode & Key inverted */

while(MC_ME.GS.B.S_MTRANS == 1); /* Wait for mode entry to complete */

while(MC_ME.GS.B.S_CURRENT_MODE != 0x3); /* Check DRUN mode has been entered */

/* 6. Configure PLL0 for required 200MHz self-test frequency: */

/* a. Configure PLL0 to provide 100MHz at its PHI output: (values depend on XOSC frequency). */

//PLLDIG_PLL0DV =

PLLDIG.PLL0DV.B.RFDPHI1 = 8;

PLLDIG.PLL0DV.B.RFDPHI = 4;

PLLDIG.PLL0DV.B.PREDIV = 1;

PLLDIG.PLL0DV.B.MFD = 25;

/*Select XOSC as PLL0's reference clock*/

MC_CGM.AC3_SC.B.SELCTL=1;

/* 7. Configure DRUN mode to turn on PLL0 and select PLL0 PHI to source SYS_CLK: */

MC_ME.DRUN_MC.B.XOSCON=1;/*Enable XOSC:*/

MC_ME.DRUN_MC.B.PLL0ON=1;/*Enable PLL0:*/

MC_ME.DRUN_MC.B.PLL1ON=0;/*Disable PLL1:*/

MC_ME.DRUN_MC.B.SYSCLK=2;/*Select PLL0 PHI as the SYS_CLK clock source*/

/* 8. Activate new configuration by performing mode change to DRUN: */

// MC_ME.MCTL.B.TARGET_MODE=3;

MC_ME.MCTL.R = 0x30005AF0; /* Mode & Key */

MC_ME.MCTL.R = 0x3000A50F; /* Mode & Key inverted */

while(MC_ME.GS.B.S_MTRANS == 1); /* Wait for mode entry to complete */

while(MC_ME.GS.B.S_CURRENT_MODE != 0x3); /* Check DRUN mode has been entered */

/* 9. Select PLL0 PHI to source all auxiliary clocks used during self-test */

MC_CGM.AC0_SC.B.SELCTL=2;

MC_CGM.AC5_SC.B.SELCTL=2;

}

/******************************************************//*!

* @par Description

* This function init all shutdown selftest registers and start shutdown selftest.

* @param NULL

* @return NULL

********************************************************/

static void ShutDownSelfTest_Init()

{

STCU.SKC.R = 0x753F924E;

STCU.SKC.R = 0x8AC06DB1;

/*2 :configure all STCU MBn CTRL register:*/

STCU_MB0_CTRL =0X91000000;

STCU_MB1_CTRL =0x98000000;

STCU_MB2_CTRL =0x93000000;

STCU_MB3_CTRL =0x94000000;

STCU_MB4_CTRL =0x95000000;

STCU_MB5_CTRL =0x96000000;

STCU_MB6_CTRL =0x97000000;

STCU_MB7_CTRL =0x10000000;

STCU_MB8_CTRL =0x99000000;

STCU_MB9_CTRL =0x9a000000;

STCU_MB10_CTRL =0x9b000000;

STCU_MB11_CTRL =0x9c000000;

STCU_MB12_CTRL =0x9d000000;

STCU_MB13_CTRL =0x9e000000;

STCU_MB14_CTRL =0x9f000000;

STCU_MB15_CTRL =0xa0000000;

STCU_MB16_CTRL =0xa1000000;

STCU_MB17_CTRL =0xa2000000;

STCU_MB18_CTRL =0xa3000000;

STCU_MB19_CTRL =0xa4000000;

STCU_MB20_CTRL =0xa5000000;

STCU_MB21_CTRL =0xa6000000;

STCU_MB22_CTRL =0xa7000000;

STCU_MB23_CTRL =0xa8000000;

STCU_MB24_CTRL =0xa9000000;

STCU_MB25_CTRL =0xaa000000;

STCU_MB26_CTRL =0x00000000;

/*3:config stcu_cfg register*/

STCU_CFG = 0X12000008;

/*4:configure all STCU_Lbn_Ctrl register*/

STCU_LB0_CTRL = 0x83031107;

STCU_LB1_CTRL = 0X82031107;

STCU_LB2_CTRL = 0X7F031107;

STCU_LB3_CTRL = 0X01031107;

/*5:configure all STCU_LBnMISRELSW /STCU_LBnMISREHSW register*/

STCU_LB0_PCS = 0x00006590;

STCU_LB1_PCS = 0x00000708;

STCU_LB2_PCS = 0x00000B00;

STCU_LB3_PCS = 0x00000740;

STCU_LB0_MISRELSW = 0xe19ee01f;

STCU_LB1_MISRELSW = 0xf1b392f7;

STCU_LB2_MISRELSW = 0xc0129454;

STCU_LB3_MISRELSW = 0xe0d719d0;

STCU_LB0_MISREHSW = 0xAA0EE288;

STCU_LB1_MISREHSW = 0x18916197;

STCU_LB2_MISREHSW = 0xDE0D037E;

STCU_LB3_MISREHSW = 0x694A0066;

/*6:configure all STCU_WDG register*/

STCU_WDG = 0x00060000;

/*7:configure STCU_LBRMSW register*/

STCU_LBRMSW = 0x0000000f;

/*8:configure DCL_IPS0 register*/

DCL_IPS0 = 0x03008214;

/*configure the STCU_RUNSW register ---- start the shutdown self-test*/

STCU_RUNSW = 0x00000301;

//wait the shutdown self-test finished

while (STCU.RUNSW.B.RUNSW == 1);

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For different cuts you need different MISR values.

For 1N15P use following:

STCU_LB0_MISREL | 0x8CBF311B |

STCU_LB1_MISREL | 0xAC435093 |

STCU_LB2_MISREL | 0x37732C00 |

STCU_LB3_MISREL | 0xB4B9D509 |

STCU_LB0_MISREH | 0xCD9077D8 |

STCU_LB1_MISREH | 0x01599F6C |

STCU_LB2_MISREH | 0x23EA1647 |

STCU_LB3_MISREH | 0xF3A1B551 |

We have created ticket for reference manual update.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For different cuts you need different MISR values.

For 1N15P use following:

STCU_LB0_MISREL | 0x8CBF311B |

STCU_LB1_MISREL | 0xAC435093 |

STCU_LB2_MISREL | 0x37732C00 |

STCU_LB3_MISREL | 0xB4B9D509 |

STCU_LB0_MISREH | 0xCD9077D8 |

STCU_LB1_MISREH | 0x01599F6C |

STCU_LB2_MISREH | 0x23EA1647 |

STCU_LB3_MISREH | 0xF3A1B551 |

We have created ticket for reference manual update.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

where we can find the ref manual?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can find on our web page all available documentation.

http://cache.nxp.com/files/32bit/doc/ref_manual/MPC5744PRM.pdf?fsrch=1&sr=4&pageNum=1

Peter