- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: S32R294 Enet Rx IRQ not entered

S32R294 Enet Rx IRQ not entered

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32R294 Enet Rx IRQ not entered

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

S32R294 Enet Rx IRQ not entered

We found a problem that we use MAC:S32R294 ENET with PHY:88Q2110 to transefer 1000Base-T1 ethernet packages.

MCU sometimes received some wrong data cause of the channel disturbance on 1000Base-T1. Sometimes the data bytes is wrong, and other times the packages are spliced unintendeely.

The problem is that, once the BABR bit is set in EIR, the receive frame/buffer interrupt can not enter any longer, althrough the receive counter in statistics register is added.

We try to clear the BABR bit in error irq, but it helps nothing. How to solve this problem? Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

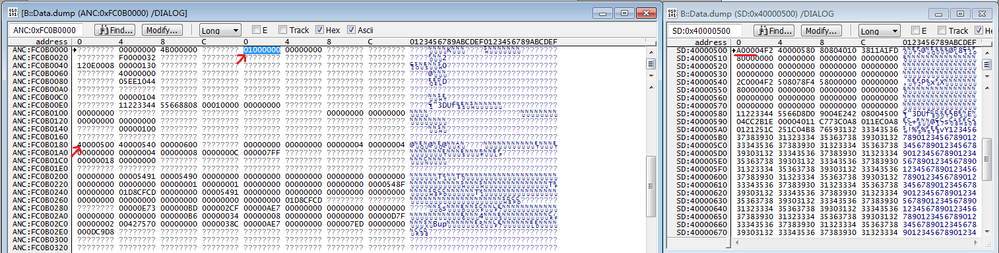

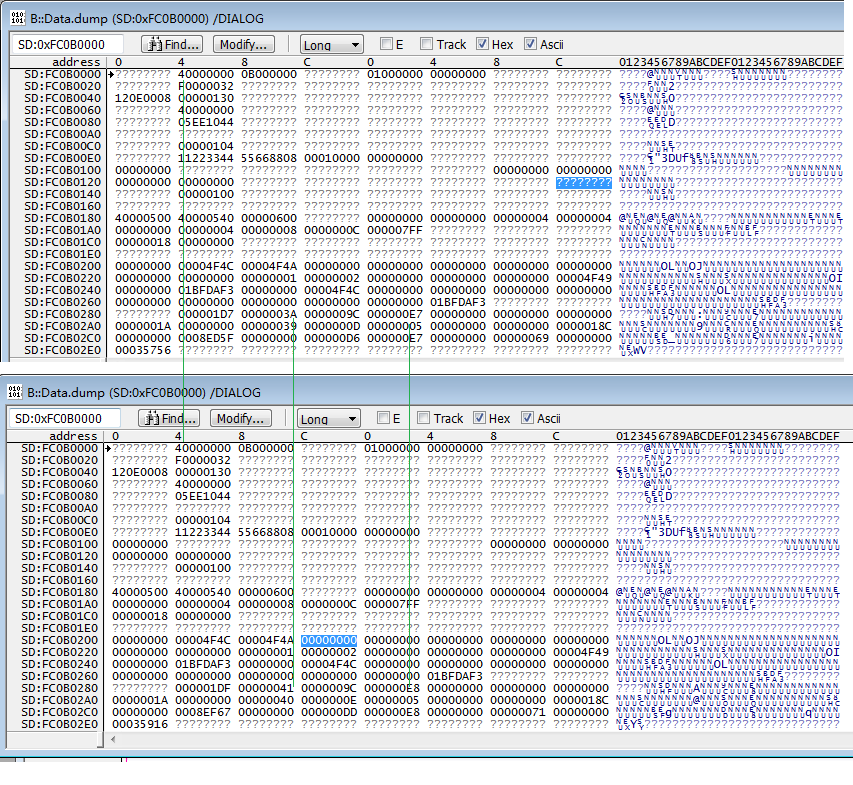

We compare the module dump(start at 0xFC080000), the module memory dump in the failure situtation is same as the dump memory once enet finish to initialize itself, excepet for statistics registers.

The icache and dcache is disable at startup.s

Dest, Source MAC address is checked(work in PROMISCUOUS_MODE can reproduce the same problem).

New finding is that , this problem can reproduce even if there is no error event during the whole test, but rx event can not entered after enet receive ethernet frames for a period of time.But, the rx statistic register add normally at this time.

So we suppose that when a disturbance on a "special position in the ethernet frame", enet receive the frame, and after that the enet state machine might to be locked.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

last idea I have...use more descriptors in the ring.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr, thanks so much for your support. We will try to investigate and do what we can except it is a module design problem locks the module if a speical frame received.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

I reproduce the problem, and check both of RxBD[E] and RDAR are set.

But the rx interrupt event still not entered.

The rxbd dump after reproduce the problem as following.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

descriptor looks normal, I think. Further hints:

- compare configuration/registers upon init and after issue appears

- be sure descriptors and buffers are not cached

- be sure it is not address check issue

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

do you clear BABR properly, means just BABR bit?

After that, do you have still some RX descriptor empty a ready for receiving, i.e. having RxDB[E] set and RDAR bit set?

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Petr,

After this siutuation occurs(rx event flag do not set any longer), I pause the MCU by debugger, and dump the ENET module. Then I send a frame on my PC, and dump the ENET module again. The rx counter in register is able to see it is increased. But no rx event set in interrupt flag during the test.