- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Good Morning,

I have 2 issues with programming the MPC5777C.

First One:

-> I want tu use the CAN_FD Option from M_CAN_0 (ISO CAN Works already)

so i Change the Parameter for can FD with and withouth Bitrate switching from example.

In my Init i wait for CCCR.INIT and CCCR.CCE for Setting 0.

After this Operation, i make the cmr request and set the can Mode with cme. The CCCR.CME bit is set in Expression view. On the other side the CCCE.FDBS and CCCR.FDO bits for the request are set no time.

#if XXX_MCAN_L_BRS_DEF

M_CAN_0.CCCR.B.CMR = 0x2; // enable CAN FD with bit rate switching

M_CAN_0.CCCR.B.CME = 0x2;

M_CAN_0.BTP.B.BRP = 1u; //4

M_CAN_0.BTP.B.SJW = 3u;

M_CAN_0.BTP.B.TSEG1 = 4u; //12

M_CAN_0.BTP.B.TSEG2 = 2u; //0

M_CAN_0.FBTP.B.FBRP = 0x0u;

M_CAN_0.FBTP.B.FSJW = 0x3u;

M_CAN_0.FBTP.B.FTSEG1 = 0x4u;

M_CAN_0.FBTP.B.FTSEG2 = 0x2u;

#else

M_CAN_0.CCCR.B.CMR = 0x1; // enable CAN FD without bit rate switching

M_CAN_0.CCCR.B.CME = 0x1;

M_CAN_0.BTP.R = 0x00011E77; // Set time quanta for 0.5Mbps

M_CAN_0.BTP.B.SJW = 5;

M_CAN_0.BTP.B.TSEG1 = 16;

M_CAN_0.BTP.B.TSEG2 = 1;

#endif

My Second issue is, that the MCAN clock is wrong. If i calculate the frequency back from my Settings, i recieve a frequency from 8.1 MHz. But i have choose xosc as clock source and Programm the extal pin in the dcf(XOSCEN=0) record as xosc. There is a 40MHz oscillator connected to this pin. So i don´t know why the freuency is so low.

SIU.SYSDIV.B.MCANSEL = 0;

SIU.HLT2.B.MCANA = 0;

SIU.HLT2.B.MCANB = 0;

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marcus,

the example posted on the community was created and tested on previous MCU cut (2N45H).

There are several changes in registers between versions, so if you have latest one, you should follow latest RM for a proper registers definition. A MPC5777CRMAD (https://www.nxp.com/docs/en/reference-manual/MPC5777CRMAD.pdf) have to be used when using 2N45H mask.

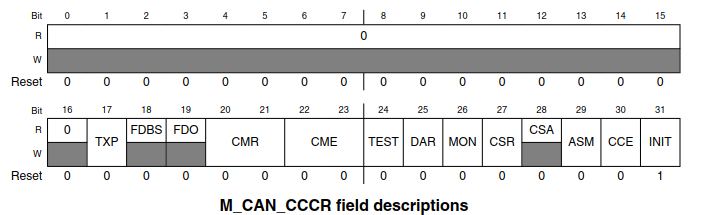

for a CCCR register

3N45H

2N45H

so the code on latest revision could be as below

// put module to Init mode

MCAN_0.CCCR.B.INIT = 0x1;

while(MCAN_0.CCCR.B.INIT == 0) { asm("nop"); }

// enable CCE bit to change config

MCAN_0.CCCR.B.CCE = 0x1;

while(MCAN_0.CCCR.B.CCE==0) { asm("nop"); }

#if BRS

MCAN_0.CCCR.B.FDOE = 0x1; // enable CAN FD

MCAN_0.CCCR.B.BRSE = 0x1; // enable bit rate switching

....

#else

MCAN_0.CCCR.B.FDOE = 0x1; // enable CAN FD

MCAN_0.CCCR.B.BRSE = 0x0; // disable bit rate switching

....

#endif

For a CAN bit timing again there is significant difference in registers. On 3N45H registers are named NBTP and DBTP (TDCR if TDC is also enabled) while on 2N45H it was BTP and FBTP. So you must set it properly to have correct timing.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marcus,

the example posted on the community was created and tested on previous MCU cut (2N45H).

There are several changes in registers between versions, so if you have latest one, you should follow latest RM for a proper registers definition. A MPC5777CRMAD (https://www.nxp.com/docs/en/reference-manual/MPC5777CRMAD.pdf) have to be used when using 2N45H mask.

for a CCCR register

3N45H

2N45H

so the code on latest revision could be as below

// put module to Init mode

MCAN_0.CCCR.B.INIT = 0x1;

while(MCAN_0.CCCR.B.INIT == 0) { asm("nop"); }

// enable CCE bit to change config

MCAN_0.CCCR.B.CCE = 0x1;

while(MCAN_0.CCCR.B.CCE==0) { asm("nop"); }

#if BRS

MCAN_0.CCCR.B.FDOE = 0x1; // enable CAN FD

MCAN_0.CCCR.B.BRSE = 0x1; // enable bit rate switching

....

#else

MCAN_0.CCCR.B.FDOE = 0x1; // enable CAN FD

MCAN_0.CCCR.B.BRSE = 0x0; // disable bit rate switching

....

#endif

For a CAN bit timing again there is significant difference in registers. On 3N45H registers are named NBTP and DBTP (TDCR if TDC is also enabled) while on 2N45H it was BTP and FBTP. So you must set it properly to have correct timing.

BR, Petr